# ADSP-21161 SHARC® Processor Hardware Reference

Revision 4.0, February 2005

Part Number 82-001944-01

Analog Devices, Inc. One Technology Way Norwood, Mass. 02062-9106

## **Copyright Information**

© 2005 Analog Devices, Inc., ALL RIGHTS RESERVED. This document may not be reproduced in any form without prior, express written consent from Analog Devices, Inc.

Printed in the USA.

#### Disclaimer

Analog Devices, Inc. reserves the right to change this product without prior notice. Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use; nor for any infringement of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under the patent rights of Analog Devices, Inc.

## Trademark and Service Mark Notice

The Analog Devices logo, EZ–Kit Lite, SHARC, the SHARC logo and VisualDSP++ are registered trademarks of Analog Devices, Inc.

All other brand and product names are trademarks or service marks of their respective owners.

## **INTRODUCTION**

| Design Advantages 1                           | -1 |

|-----------------------------------------------|----|

| Architecture Overview 1                       | -5 |

| Processor Core 1                              | -5 |

| Processing Elements 1                         | -6 |

| Program Sequence Control 1                    | -7 |

| Processor Internal Buses 1-                   | 10 |

| Processor Peripherals 1-                      | 11 |

| Dual-Ported Internal Memory (SRAM) 1-         | 11 |

| External Port 1-                              | 12 |

| I/O Processor 1-                              | 14 |

| JTAG Port 1-                                  | 16 |

| Differences From Previous SHARC Processors 1- | 16 |

| Processor Core Enhancements 1-                | 17 |

| Processor Internal Bus Enhancements 1-        | 17 |

| Memory Organization Enhancements 1-           | 18 |

| External Port Enhancements1-                  | 18 |

| Host Interface Enhancements1-                 | 18 |

| Multiprocessor Interface Enhancements 1-      | 19 |

| IO Architecture Enhancements               | 1-19 |

|--------------------------------------------|------|

| DMA Controller Enhancements                | 1-19 |

| Link Port Enhancements                     | 1-19 |

| Instruction Set Enhancements               | 1-20 |

| For More Information About Analog Products | 1-21 |

| For Technical or Customer Support          | 1-22 |

| What's New in This Manual                  | 1-22 |

| Related Documents                          | 1-23 |

| Conventions                                | 1-24 |

|                                            |      |

## **PROCESSING ELEMENTS**

| Setting Computational Modes 2-4                |

|------------------------------------------------|

| 32-Bit (Normal Word) Floating-Point Format 2-4 |

| 40-Bit Floating-Point Format 2-5               |

| 16-Bit (Short Word) Floating-Point Format 2-6  |

| 32-Bit Fixed-Point Format 2-6                  |

| Rounding Mode 2-7                              |

| Using Computational Status 2-8                 |

| Arithmetic Logic Unit (ALU) 2-9                |

| ALU Operation 2-9                              |

| ALU Saturation                                 |

| ALU Status Flags 2-11                          |

| ALU Instruction Summary 2-12                   |

| Multiply—Accumulator (Multiplier) 2-15         |

| Multiplier Operation 2-15                      |

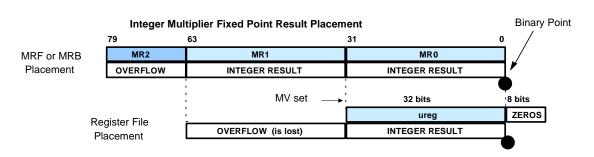

| Multiplier (Fixed-Point) Result Register 2- | -16 |

|---------------------------------------------|-----|

| Multiplier Status Flags 2-                  | -19 |

| Multiplier Instruction Summary2-            | -20 |

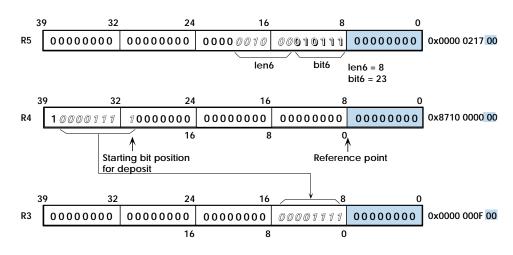

| Barrel-Shifter (Shifter) 2-                 | -23 |

| Shifter Operation2-                         | -23 |

| Shifter Status Flags2-                      | -27 |

| Shifter Instruction Summary 2-              | -28 |

| Data Register File 2-                       | -30 |

| Alternate (Secondary) Data Registers 2-     | -32 |

| Multifunction Computations 2-               | -34 |

| Secondary Processing Element (PEy) 2-       | -37 |

| Dual Compute Units Sets 2-                  | -39 |

| Dual Register Files 2-                      | -42 |

| Dual Alternate Registers 2-                 | -43 |

| SIMD (Computational) Operations 2-          | -43 |

| SIMD And Status Flags 2-                    | -46 |

|                                             |     |

## PROGRAM SEQUENCER

| 3-11 |

|------|

| 3-11 |

| 3-13 |

| 3-15 |

| 3-15 |

|      |

| Restrictions and Limitations When Using Delayed Branches | 3-19 |

|----------------------------------------------------------|------|

| Loops and Sequencing                                     |      |

| Restrictions on Ending Loops                             | 3-25 |

| Restrictions on Short Loops                              | 3-26 |

| Loop Address Stack                                       | 3-29 |

| Loop Counter Stack                                       | 3-30 |

| Interrupts and Sequencing                                | 3-34 |

| Sensing Interrupts                                       | 3-40 |

| Masking Interrupts                                       | 3-41 |

| Latching Interrupts                                      | 3-42 |

| Stacking Status During Interrupts                        | 3-44 |

| Nesting Interrupts                                       | 3-45 |

| Reusing Interrupts                                       | 3-47 |

| Interrupting IDLE                                        | 3-48 |

| Multiprocessing Interrupts                               | 3-49 |

| Timer and Sequencing                                     | 3-50 |

| Stacks and Sequencing                                    | 3-52 |

| Conditional Sequencing                                   | 3-53 |

| SIMD Mode and Sequencing                                 | 3-57 |

| Conditional Compute Operations                           | 3-58 |

| Conditional Branches and Loops                           | 3-59 |

| Conditional Data Moves                                   | 3-59 |

| Case 1: Complementary Register Pair Data Move            | 3-60 |

| Case 2: Uncomplemented–to–Complementary<br>Register Move          | 3-63 |

|-------------------------------------------------------------------|------|

| Case 3: Complementary Register => Uncomplimentary<br>Register     | 3-64 |

| Case 4: Data Move Involves External Memory or<br>IOP Memory Space | 3-65 |

| Conditional DAG Operations                                        | 3-66 |

## DATA ADDRESS GENERATOR

| Setting DAG Modes                   | 4-2  |

|-------------------------------------|------|

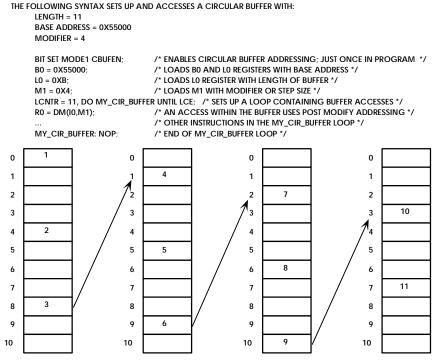

| Circular Buffering Mode             | 4-4  |

| Broadcast Loading Mode              | 4-5  |

| Alternate (Secondary) DAG Registers | 4-6  |

| Bit-reverse Addressing Mode         | 4-8  |

| Using DAG Status                    | 4-8  |

| DAG Operations                      | 4-9  |

| Addressing With DAGs                | 4-10 |

| Addressing Circular Buffers         | 4-12 |

| Modifying DAG Registers             | 4-17 |

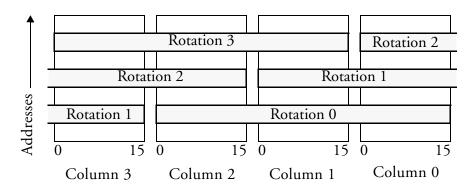

| Addressing in SISD and SIMD Modes   | 4-18 |

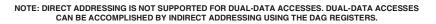

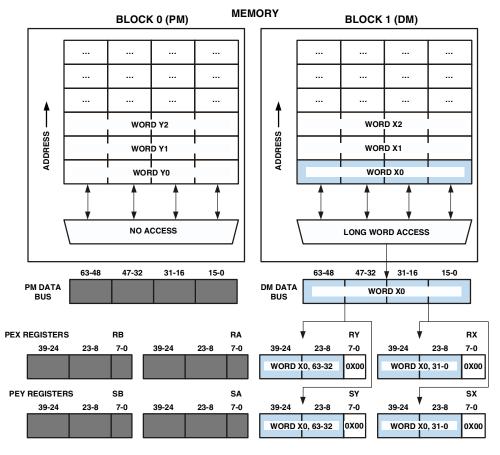

| DAGs, Registers, and Memory         | 4-18 |

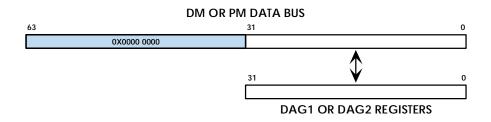

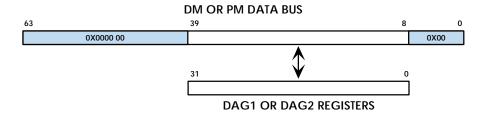

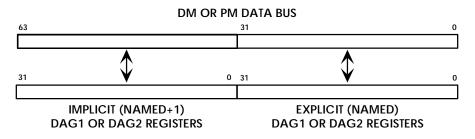

| DAG Register-to-Bus Alignment       | 4-19 |

| DAG Register Transfer Restrictions  | 4-21 |

| DAG Instruction Summary             | 4-23 |

## MEMORY

| Internal Memory 5-2                                 |

|-----------------------------------------------------|

| External Memory 5-2                                 |

| Processor Architecture                              |

| Off-Chip Memory and Peripherals Interface 5-6       |

| Buses                                               |

| Internal Address and Data Buses 5-7                 |

| Internal Data Bus Exchange 5-10                     |

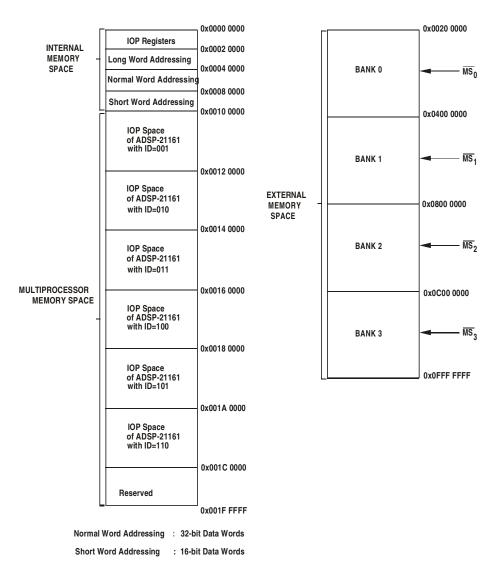

| ADSP-21161 Memory Map 5-16                          |

| Internal Memory 5-16                                |

| Multiprocessor Memory 5-19                          |

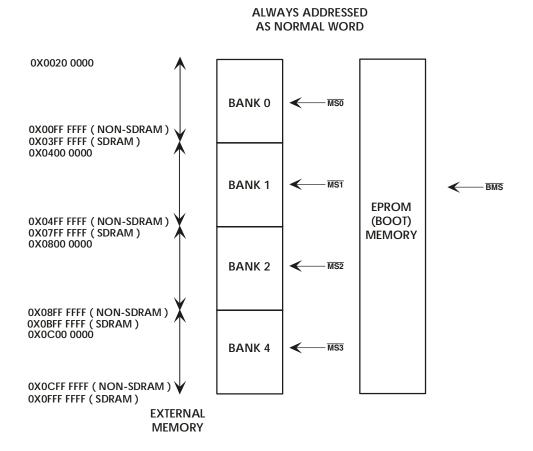

| External Memory 5-22                                |

| Shadow Write FIFO 5-24                              |

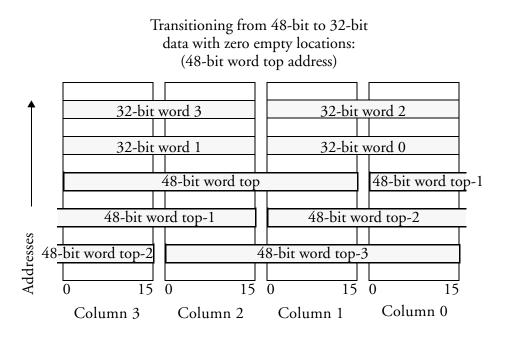

| Memory Organization and Word Size 5-25              |

| Placing 32-Bit Words and 48-Bit Words 5-25          |

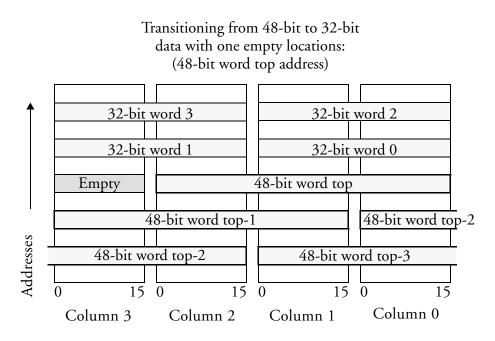

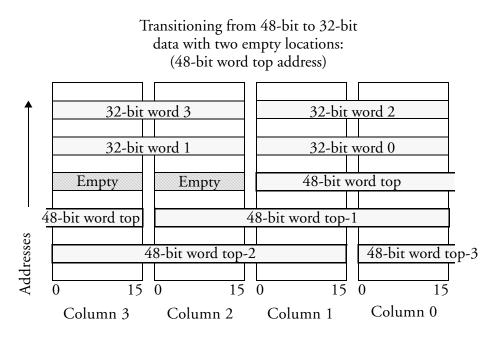

| Mixing 32-Bit and 48-Bit Words 5-26                 |

| Restrictions on Mixing 32-Bit and 48-Bit Words 5-28 |

| 48-Bit Word Allocation 5-31                         |

| Setting Data Access Modes 5-32                      |

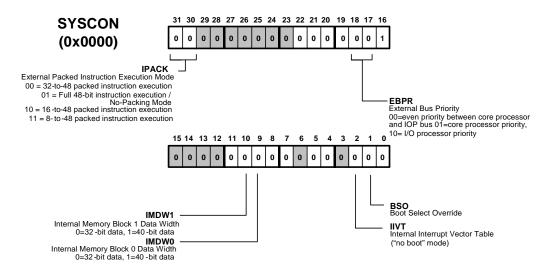

| SYSCON Register Control Bits 5-32                   |

| Mode 1 Register Control Bits 5-34                   |

| Mode 2 Register Control Bits 5-34                   |

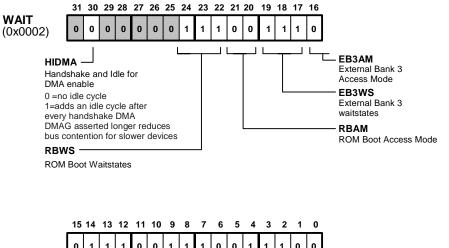

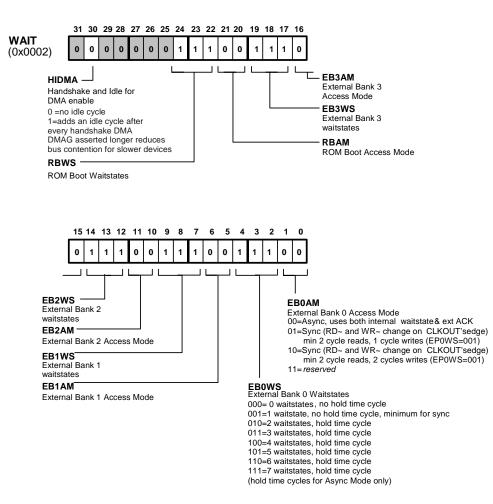

| Wait Register Control Bits 5-34                     |

| Using Boot Memory 5-35                              |

| Reading From Boot Memory                          | 5-35 |

|---------------------------------------------------|------|

| Writing to Boot Memory                            | 5-36 |

| Internal Interrupt Vector Table                   | 5-37 |

| Internal Memory Data Width                        | 5-37 |

| Memory Bank Size                                  | 5-38 |

| External Bus Priority                             | 5-39 |

| Secondary Processor Element (PEy)                 | 5-39 |

| Broadcast Register Loads                          | 5-40 |

| Illegal I/O Processor Register Access             | 5-41 |

| Unaligned 64-Bit Memory Access                    | 5-41 |

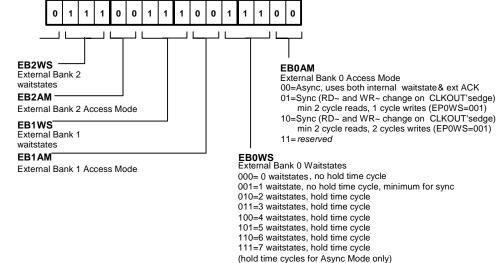

| External Bank X Access Mode                       | 5-42 |

| External Bank X Waitstates                        | 5-45 |

| Using Memory Access Status                        | 5-46 |

| Accessing Memory                                  | 5-46 |

| Access Word Size                                  | 5-47 |

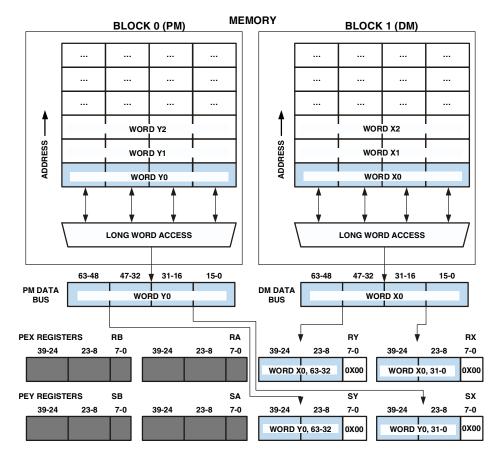

| Long Word (64-Bit) Accesses                       | 5-48 |

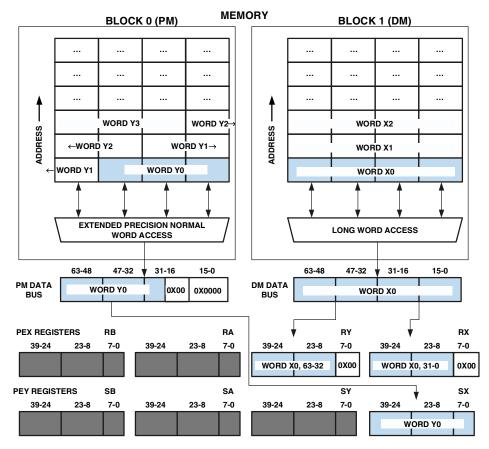

| Instruction Word (48-Bit) and Extended-Precision  |      |

| Normal Word (40-Bit) Accesses                     | 5-50 |

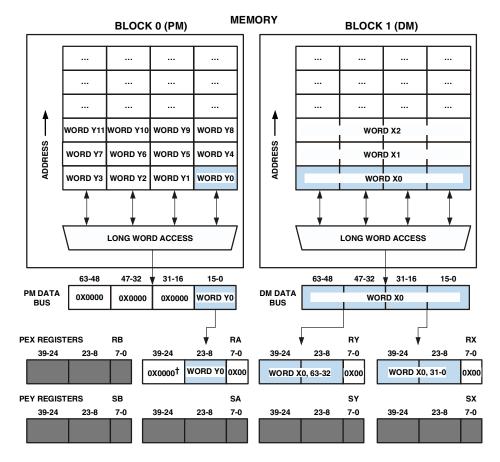

| Normal Word (32-Bit) Accesses                     | 5-50 |

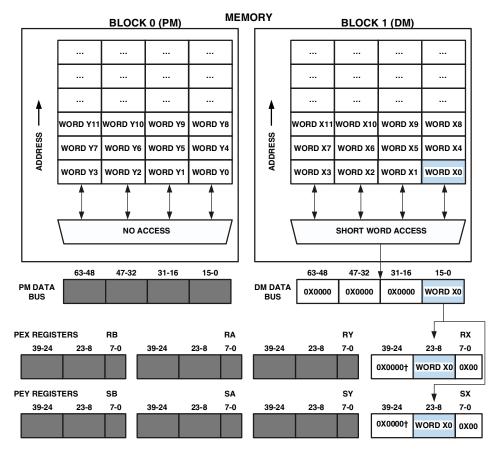

| Short Word (16-Bit) Accesses                      | 5-51 |

| SISD, SIMD, and Broadcast Load Modes              | 5-51 |

| Single and Dual Data Accesses                     | 5-52 |

| Data Access Options                               | 5-52 |

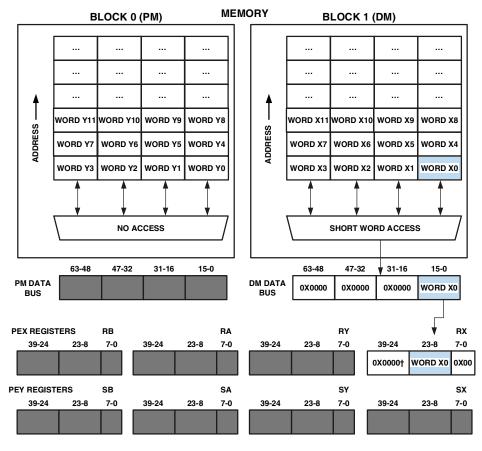

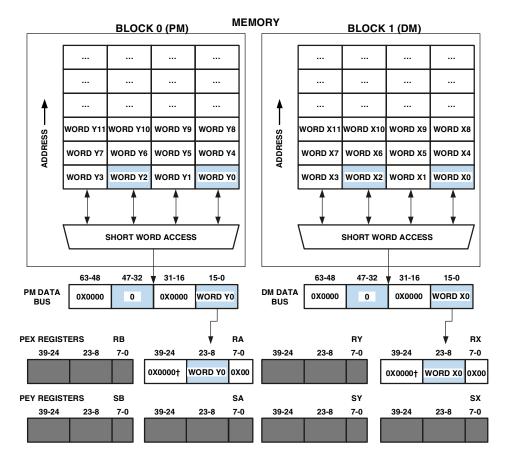

| Short Word Addressing of Single Data in SISD Mode | 5-54 |

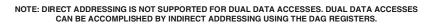

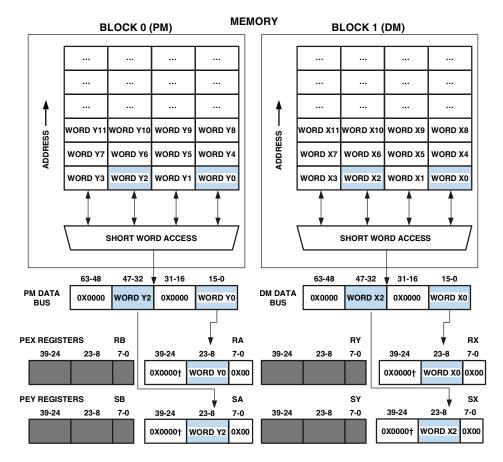

| Short Word Addressing of Single Data in SIMD Mode | 5-56 |

| Short Word Addressing of Dual-Data in SISD Mode                        | 5-58 |

|------------------------------------------------------------------------|------|

| Short Word Addressing of Dual-Data in SIMD Mode                        | 5-60 |

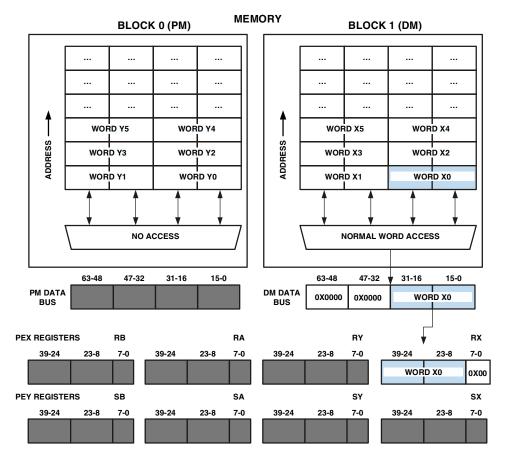

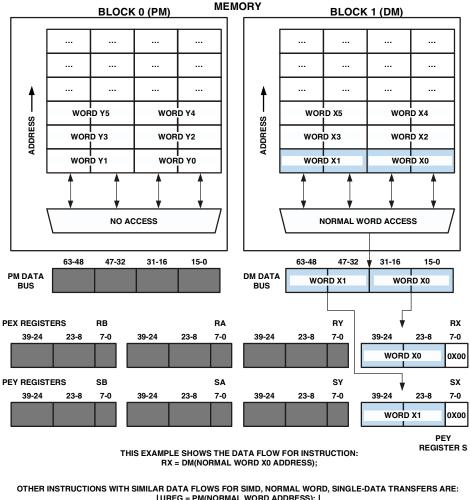

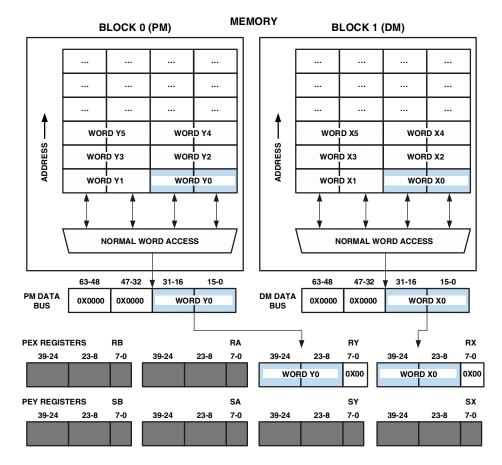

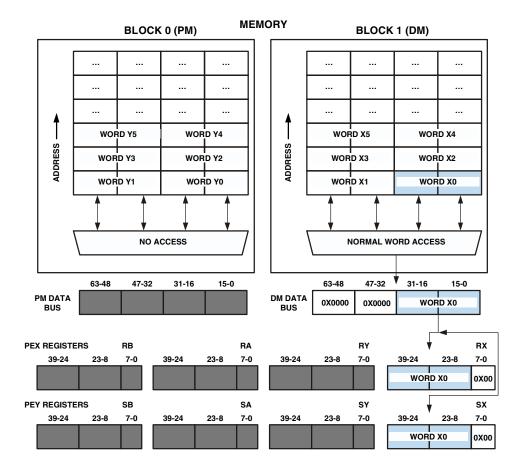

| 32-Bit Normal Word Addressing of Single Data in SISD Mode              | 5-62 |

| 32-Bit Normal Word Addressing of Single Data in SIMD Mode              | 5-64 |

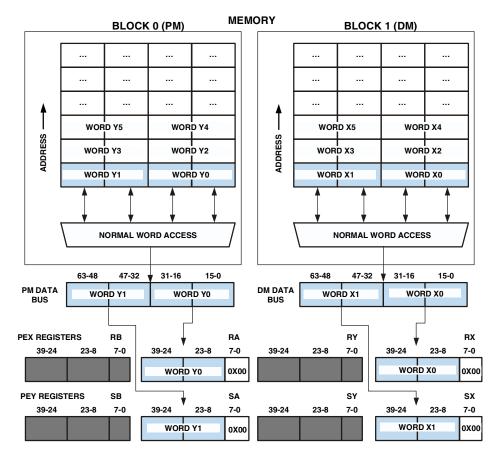

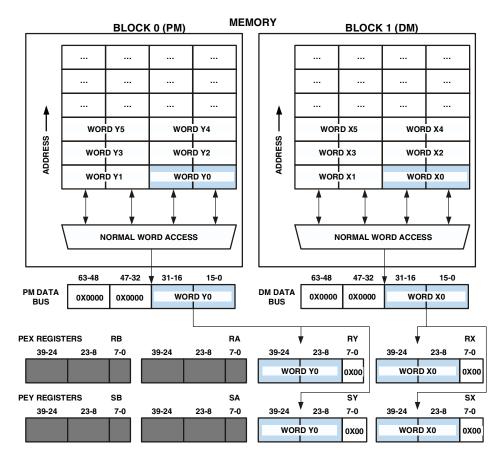

| 32-Bit Normal Word Addressing of Dual Data in SISD Mode                | 5-66 |

| 32-Bit Normal Word Addressing of Dual Data in SIMD Mode                | 5-68 |

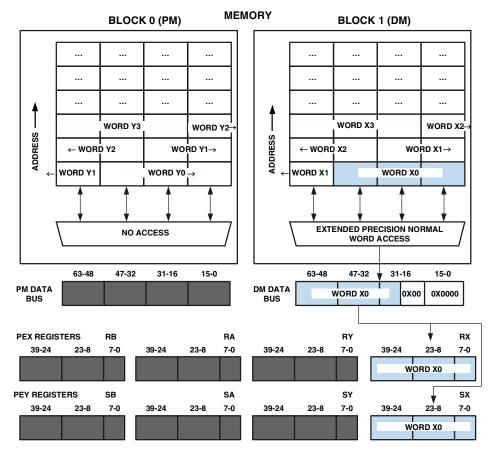

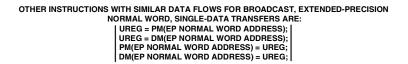

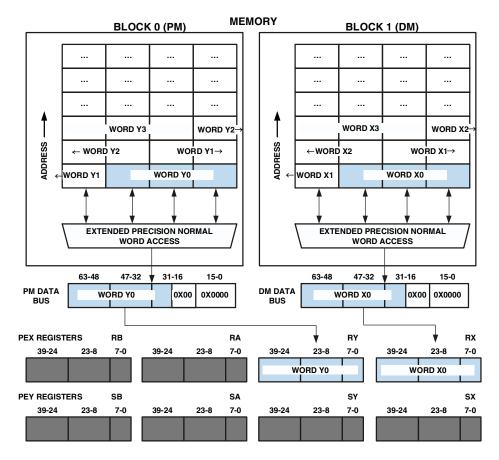

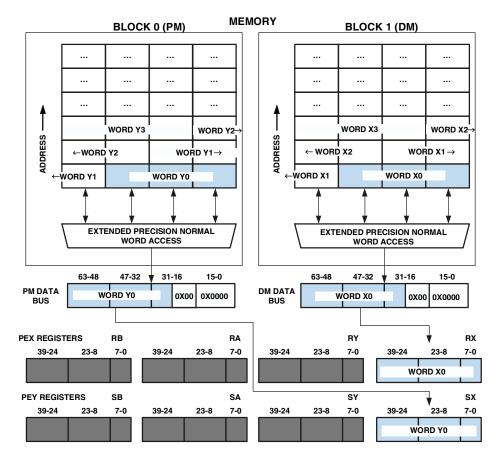

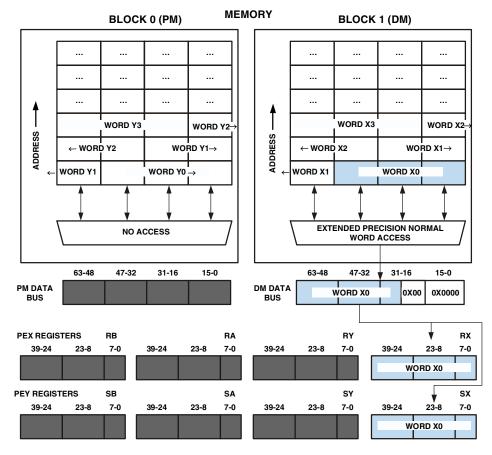

| Extended Precision Normal Word Addressing of<br>Single Data            | 5-70 |

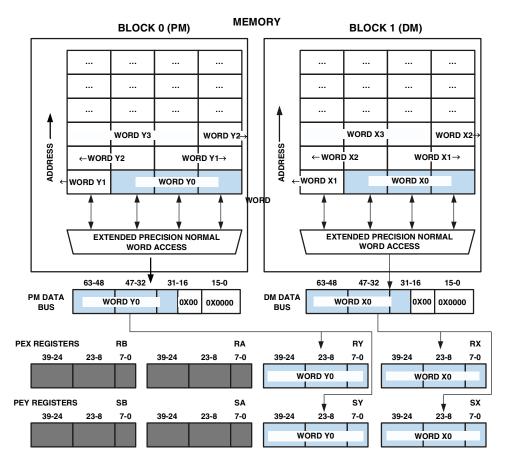

| Extended Precision Normal Word Addressing of Dual<br>Data in SISD Mode | 5-72 |

| Extended-Precision Normal Word Addressing of Dual<br>Data in SIMD Mode | 5-74 |

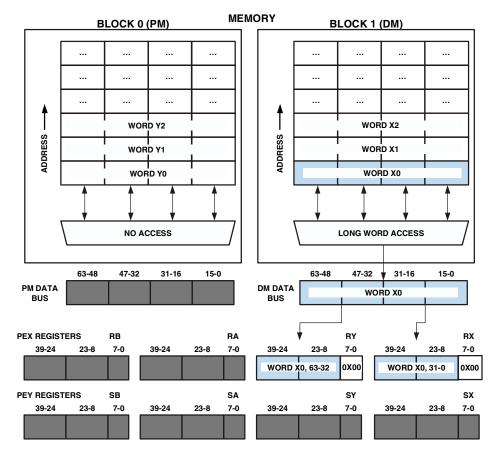

| Long Word Addressing of Single Data                                    | 5-76 |

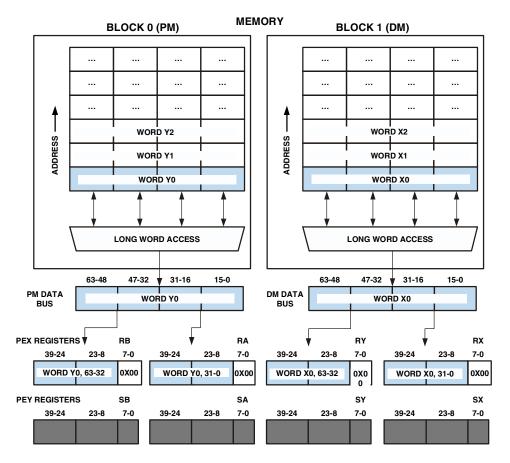

| Long Word Addressing of Dual Data in SISD Mode                         | 5-78 |

| Long Word Addressing of Dual Data in SIMD Mode                         | 5-80 |

| Mixed Word Width Addressing of Dual Data in SISD Mode                  | 5-82 |

| Mixed Word Width Addressing of Dual Data in SIMD Mode                  | 5-84 |

| Broadcast Load Access                                                  | 5-86 |

| Shadow Write FIFO Considerations in SIMD Mode                          | 5-95 |

| Arranging Data in Memory                                               | -100 |

| Executing Instructions From External Memory                            | -101 |

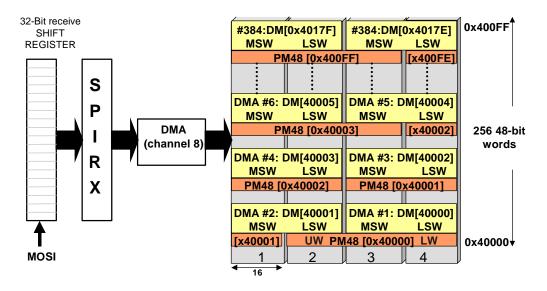

| 32- to 48-Bit Packing Address Generation Scheme 5                  | 5-109                            |

|--------------------------------------------------------------------|----------------------------------|

| Total Program Size (32- to 48-Bit Packing) 5                       | 5-110                            |

| 16- to 48-Bit Packing Address Generation Scheme 5                  | 5-111                            |

| Total Program Size (16- to 48-Bit Packing) 5                       | 5-111                            |

| 8- to 48-Bit Packing Address Generation Scheme 5                   | 5-112                            |

| Total Program Size (8- to 48-Bit Packing) 5                        | 5-113                            |

| No Packing (48- to 48-Bit) Address Generation Scheme 5             | 5-113                            |

| <ul> <li>16- to 48-Bit Packing Address Generation Scheme</li></ul> | 5-11:<br>5-11:<br>5-11:<br>5-11: |

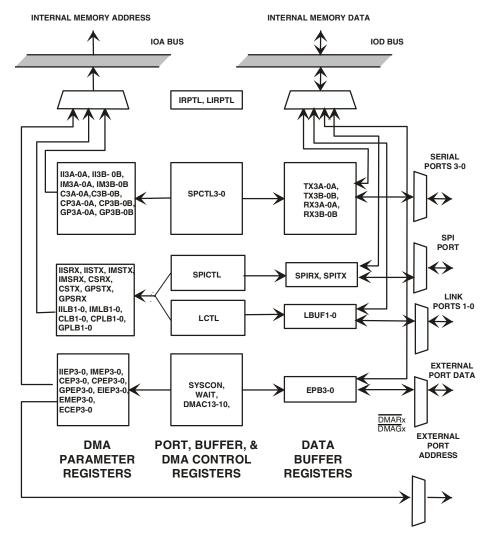

## **I/O PROCESSOR**

| DMA Channel Allocation and Priorities      | 6-16 |

|--------------------------------------------|------|

| DMA Interrupt Vector Locations             | 6-18 |

| Booting Modes                              | 6-20 |

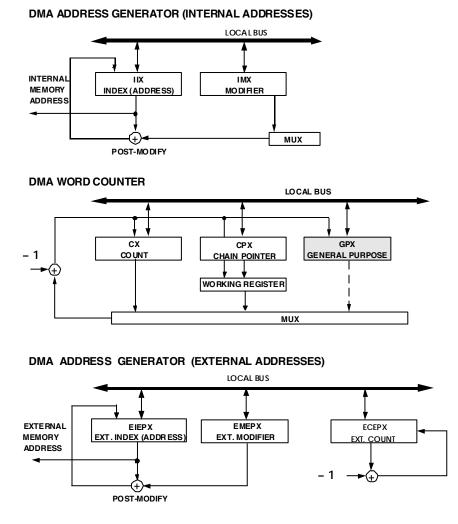

| DMA Controller Operation                   | 6-20 |

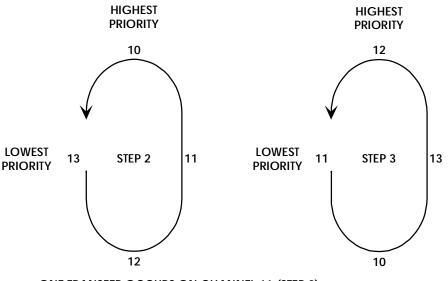

| Managing DMA Channel Priority              | 6-22 |

| Chaining DMA Processes                     | 6-25 |

| Transfer Control Block (TCB) Chain Loading | 6-26 |

| Setting Up and Starting the Chain          | 6-28 |

| Inserting a TCB in an Active Chain         | 6-28 |

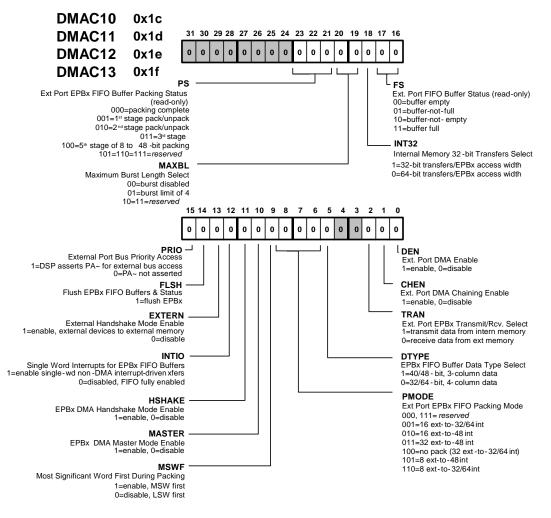

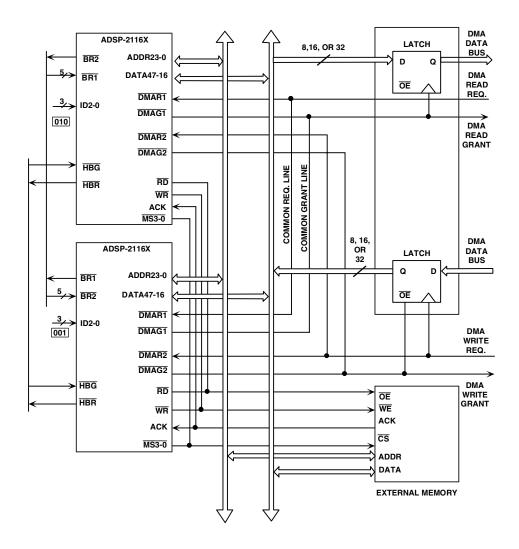

| External Port DMA                          | 6-29 |

| External Port Registers                    | 6-30 |

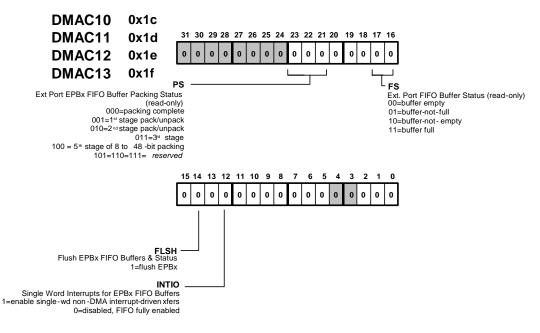

| External Port FIFO Buffers                 | 6-33 |

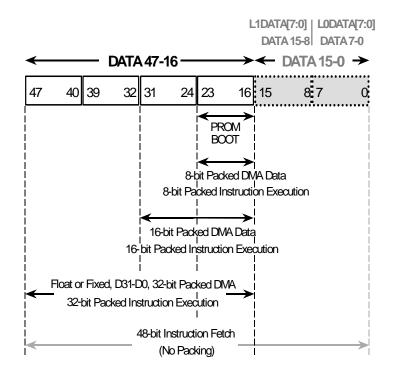

| External Port DMA Data Packing             | 6-34 |

| 32-Bit Bus Downloading                     | 6-37 |

| 16-Bit Bus Downloading                     | 6-38 |

| 8-Bit Bus Downloading                      | 6-39 |

| Boot Memory DMA Mode                   | 6-42 |

|----------------------------------------|------|

| External Port Buffer Modes             | 6-42 |

| External Port Channel Priority Modes   | 6-43 |

| External Port Channel Transfer Modes   | 6-46 |

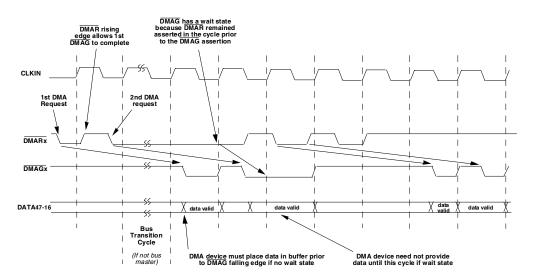

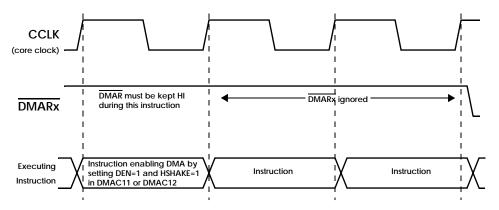

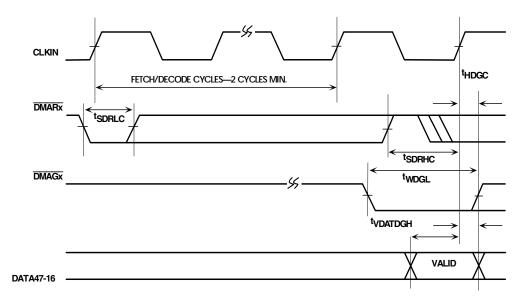

| External Port Channel Handshake Modes  | 6-47 |

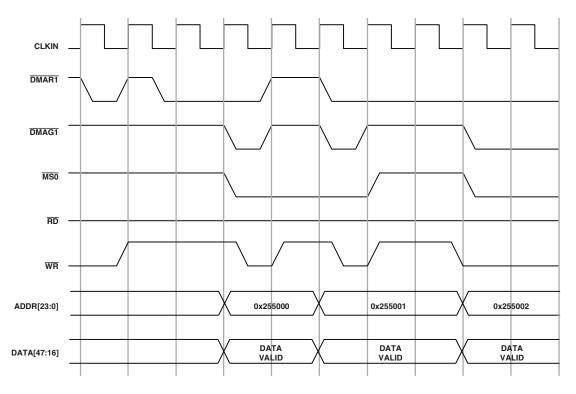

| Master Mode                            | 6-50 |

| Paced Master Mode                      | 6-54 |

| Slave Mode                             | 6-55 |

| Handshake Mode                         | 6-57 |

| DMA Handshake Idle Cycle               | 6-64 |

| External-Handshake Mode                | 6-66 |

| Setting Up External Port DMA           | 6-68 |

| Bootloading Through The External Port  |      |

| Host Processor Booting                 | 6-72 |

| PROM Booting                           | 6-74 |

| External Port DMA Programming Examples | 6-76 |

| Link Port DMA                          | 6-81 |

| Link Port Registers                    | 6-81 |

| Link Port Buffer Modes                 | 6-83 |

| Link Port Channel Priority Modes       | 6-83 |

| Link Port Channel Transfer Modes       | 6-85 |

| Setting Up Link Port DMA               | 6-86 |

| Bootloading Through The Link Port      | 6-88 |

| Link Port DMA Programming Examples     | 6-90 |

| Serial Port DMA                      |

|--------------------------------------|

| Serial Port Registers                |

| Serial Port Buffer Modes 6-97        |

| Serial Port Channel Priority Modes   |

| Serial Port Channel Transfer Modes   |

| Setting Up Serial Port DMA 6-100     |

| SPORT DMA Programming Examples 6-102 |

| SPI Port DMA                         |

| SPI Port Registers                   |

| SPI Port Buffer 6-109                |

| SPI DMA Channel Priority 6-112       |

| Setting up SPl Port DMA 6-112        |

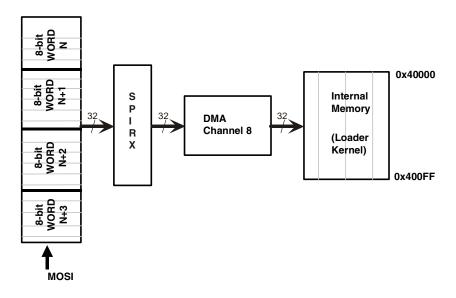

| Bootloading Through the SPI Port     |

| SPI Port DMA Programming Examples    |

| Using I/O Processor Status           |

| External Port Status                 |

| Link Port Status                     |

| Serial Port Status                   |

| SPI Port Status                      |

| Optimizing DMA Throughput            |

| Internal Memory DMA 6-139            |

| External Memory DMA 6-140            |

| System-Level Considerations          |

## **EXTERNAL PORT**

| Setting External Port Modes 7                             | 7-3 |

|-----------------------------------------------------------|-----|

| External Memory Interface 7                               | 7-3 |

| Banked External Memory 7                                  | 7-9 |

| Boot Memory 7-                                            | 10  |

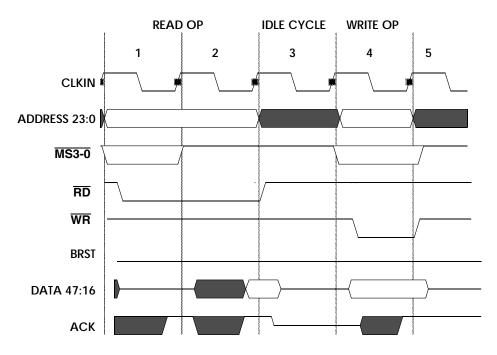

| Idle Cycle 7-                                             | 10  |

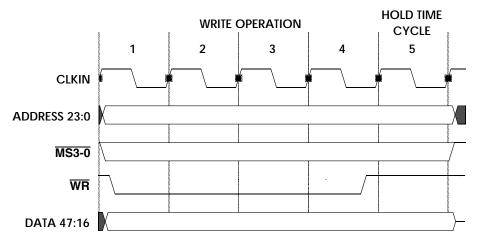

| Data Hold Cycle 7-                                        | 12  |

| Multiprocessor Memory Space Waitstates and<br>Acknowledge | 12  |

| Timing External Memory Accesses 7-                        | 13  |

| Asynchronous Mode Interface Timing 7-                     | 14  |

| Synchronous Mode Interface Timing 7-                      | 18  |

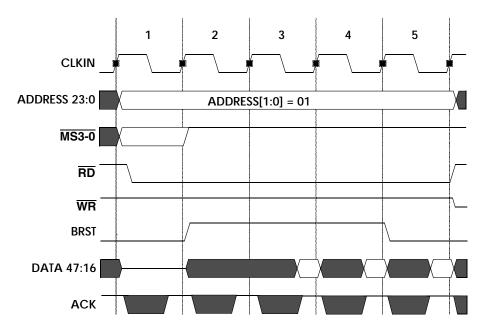

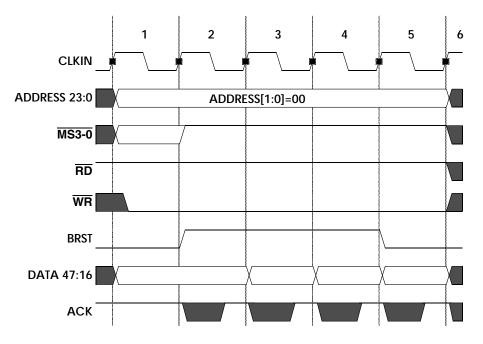

| Synchronous Burst Mode Interface Timing 7-2               | 26  |

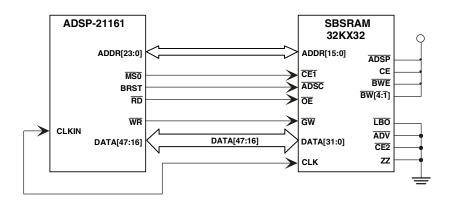

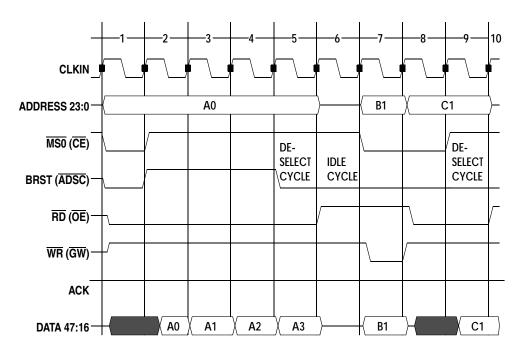

| Using External SBSRAM 7                                   | 36  |

| SBSRAM Restrictions                                       | 41  |

| Host Processor Interface                                  | 42  |

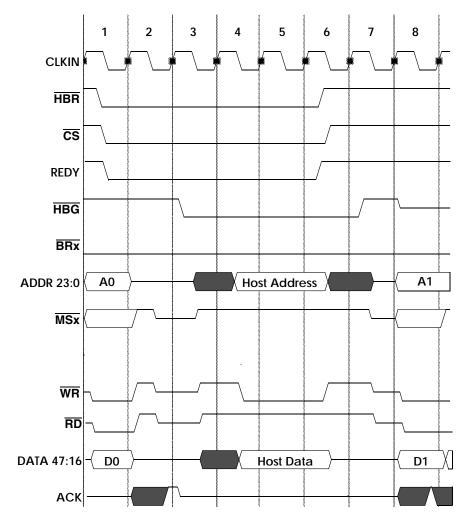

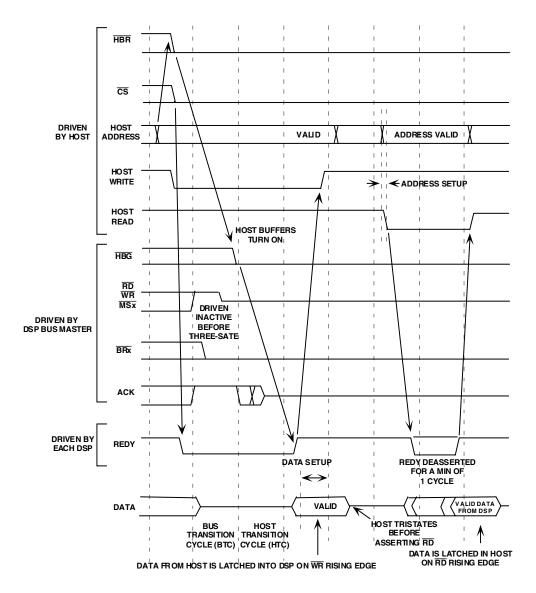

| Acquiring the Bus                                         | 44  |

| Asynchronous Transfers 7                                  | 48  |

| Host Transfer Timing 7-                                   | 51  |

| Host Interface Deadlock Resolution With SBTS              | 54  |

| Slave Reads and Writes 7-                                 | 55  |

| IOP Shadow Registers 7-:                                  | 55  |

| Instruction Transfers                                     | 56  |

| Slave Write Latency                                       | 56  |

| Slave Reads                                   | 7-57 |

|-----------------------------------------------|------|

| Broadcast Writes                              | 7-57 |

| Data Transfers Through the EPBx Buffers       | 7-58 |

| DMA Transfers                                 | 7-58 |

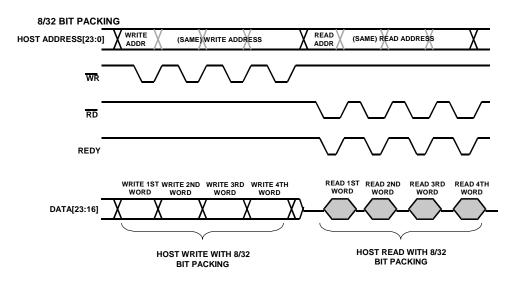

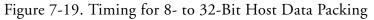

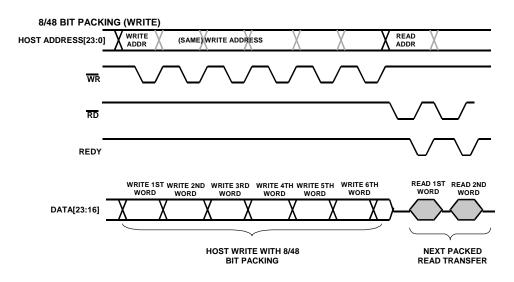

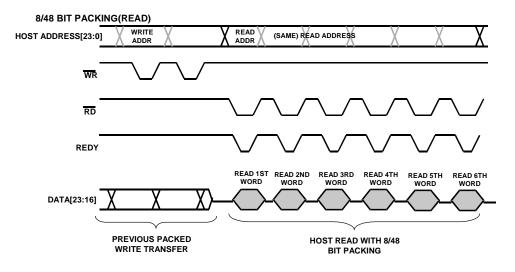

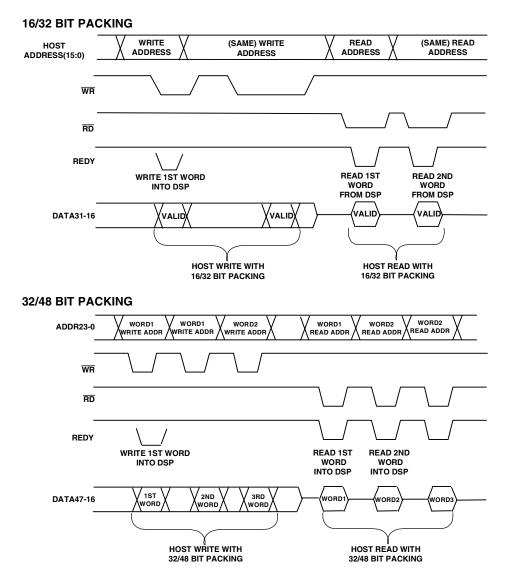

| Host Data Packing                             | 7-59 |

| Packing Mode Variations For Host Accesses     | 7-61 |

| IOP Register Host Accesses                    | 7-62 |

| LINK Port Buffer Access                       | 7-63 |

| EPBx Buffer Accesses                          | 7-64 |

| 8- to 32-Bit Data Packing                     | 7-66 |

| 16- to 32-Bit Packing                         | 7-69 |

| 48-Bit Instruction Packing                    | 7-74 |

| Host Interface Status                         | 7-76 |

| Interprocessor Messages and Vector Interrupts | 7-76 |

| Message Passing (MSGRx)                       | 7-77 |

| Host Vector Interrupts (VIRPT)                | 7-78 |

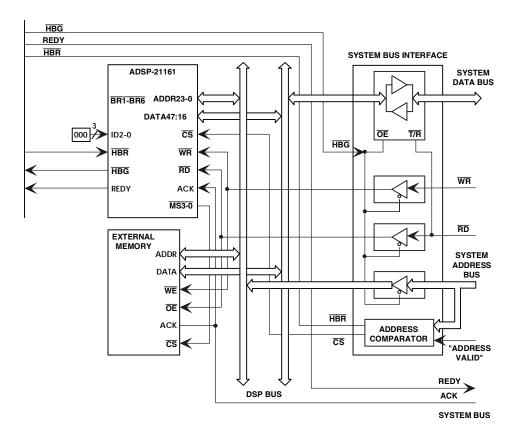

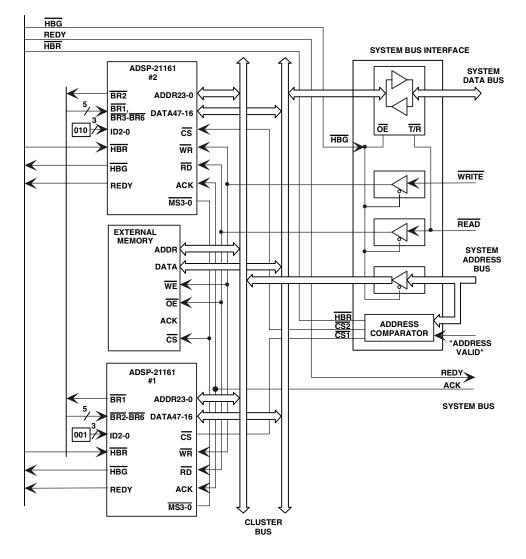

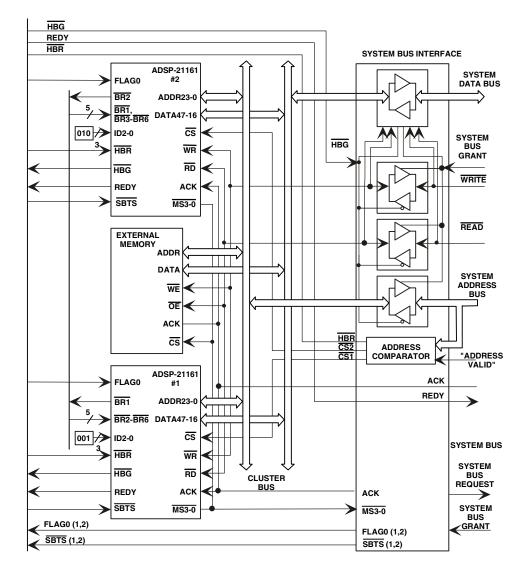

| System Bus Interfacing                        | 7-78 |

| Access to the Processor Bus – Slave Processor | 7-79 |

| Access to the System Bus – Master Processor   | 7-79 |

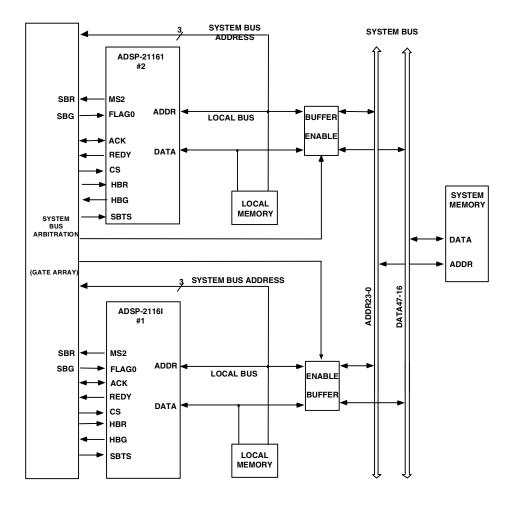

| Processor Core Access to System Bus           | 7-82 |

| Deadlock Resolution                           | 7-82 |

| DMA Access to System Bus                      | 7-84 |

| Multiprocessing With Local Memory             | 7-85 |

| ADSP-21161 to Microprocessor Interface        |      |

| Multiprocessor (MP) Interface 7-87        |

|-------------------------------------------|

| Multiprocessing System Architectures 7-90 |

| Data Flow Multiprocessing 7-90            |

| Cluster Multiprocessing 7-91              |

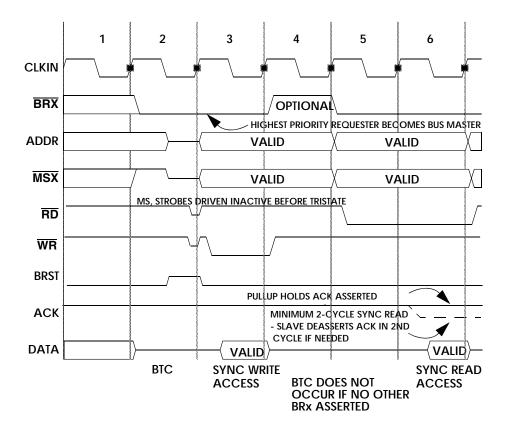

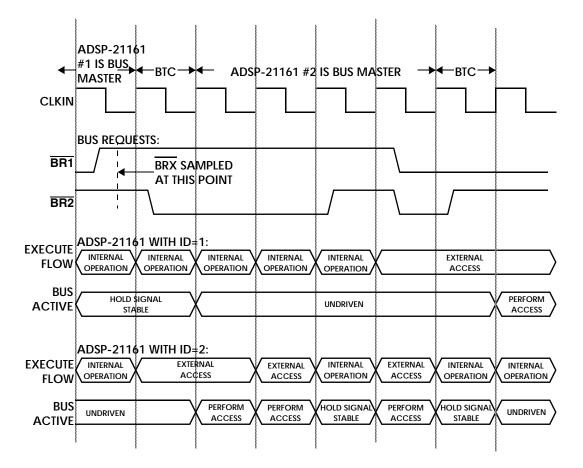

| Multiprocessor Bus Arbitration            |

| Bus Arbitration Protocol                  |

| Bus Arbitration Priority (RPBA)           |

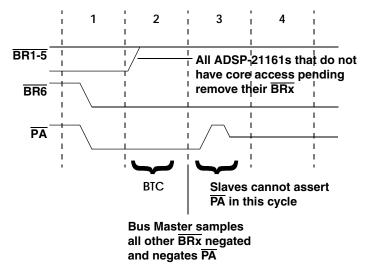

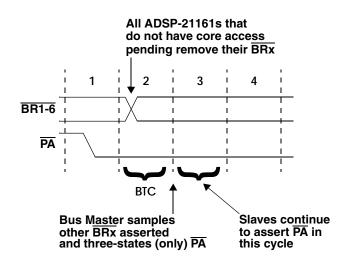

| Bus Mastership Timeout 7-101              |

| Priority Access                           |

| Bus Synchronization After Reset 7-105     |

| Booting Another processor                 |

| Multiprocessor Writes and Reads           |

| Instruction Transfers 7-110               |

| Bus Lock and Semaphores                   |

| Multiprocessor Interface Status           |

## **SDRAM INTERFACE**

| SDRAM Pin Connections                        | 8-7  |

|----------------------------------------------|------|

| SDRAM Timing Specifications                  | 8-8  |

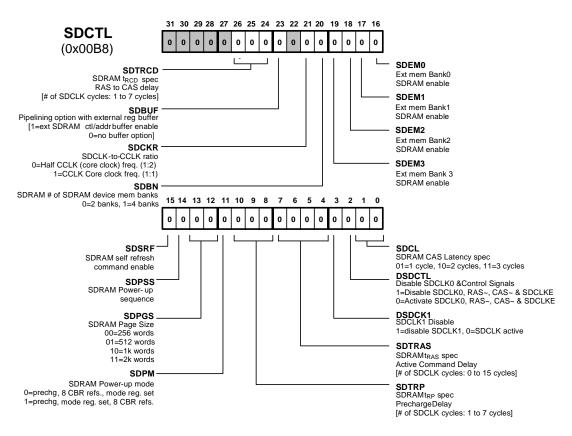

| SDRAM Control Register (SDCTL)               | 8-9  |

| SDRAM Configuration for Runtime 8            | 3-10 |

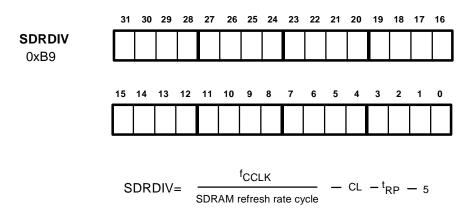

| Setting the Refresh Counter Value (SDRDIV) 8 | 3-13 |

| Setting the SDRAM Clock Enables 8            | 3-14 |

| Setting the Number of SDRAM Banks (SDBN) 8   | 3-15 |

| Setting the External Memory Bank (SDEMx) 8   | 3-16 |

|     | Setting the SDRAM Buffering Option (SDBUF)                  | 8-16 |

|-----|-------------------------------------------------------------|------|

|     | Selecting the CAS Latency Value (SDCL)                      | 8-17 |

|     | Selecting the SDRAM Page Size (SDPGS)                       | 8-18 |

|     | Setting the SDRAM Power-Up Mode (SDPM)                      | 8-19 |

|     | Starting the SDRAM Power-Up Sequence (SDPSS)                | 8-19 |

|     | Starting Self-Refresh Mode (SDSRF)                          | 8-20 |

|     | Selecting the Active Command Delay (SDTRAS)                 | 8-20 |

|     | Selecting the Precharge Delay (SDTRP)                       | 8-21 |

|     | Selecting the RAS-to-CAS Delay (SDTRCD)                     | 8-21 |

| SD  | RAM Controller Standard Operation                           | 8-22 |

|     | Understanding DAG and DMA Operation                         | 8-22 |

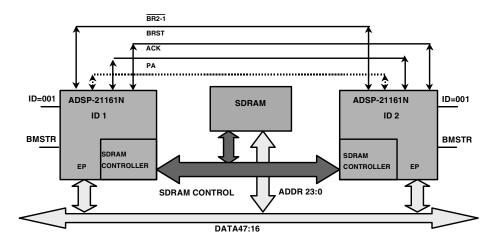

|     | Multiprocessing Operation                                   | 8-24 |

|     | Accessing SDRAM                                             | 8-25 |

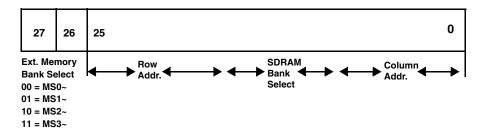

|     | Address Mapping for SDRAM                                   | 8-27 |

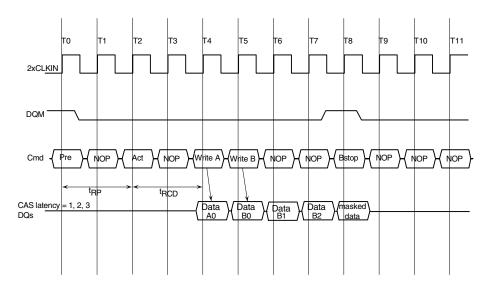

|     | Understanding DQM Operation                                 | 8-29 |

|     | Executing a Parallel Refresh Command During<br>Host Control | 8-29 |

|     | Powering Up After Reset                                     |      |

|     | 0 1                                                         |      |

| 0.0 | Entering and Exiting Self-Refresh Mode                      |      |

| SD  | RAM Controller Commands                                     |      |

|     | Bank Activate (ACT) Command                                 | 8-32 |

|     | Mode Register Set (MRS)                                     | 8-32 |

|     | Precharge Command (PRE)                                     | 8-33 |

|     | Read/Write Command                                          | 8-34 |

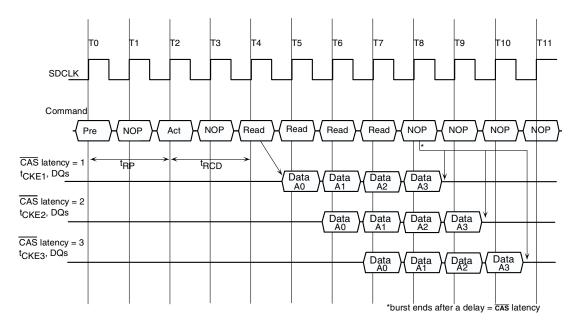

|     | Read Commands                                               | 8-34 |

| Write Commands                             | 8-36 |

|--------------------------------------------|------|

| DMA Transfers                              | 8-37 |

| Refresh (REF) Command                      | 8-37 |

| Setting the Delay Between Refresh Commands | 8-37 |

| Understanding Multiprocessing Operation    | 8-38 |

| Self Refresh Command (SREF)                | 8-39 |

| Programming Example                        | 8-40 |

|                                            |      |

## LINK PORTS

| Link Port to Link Buffer Assignment                | 9-3  |

|----------------------------------------------------|------|

| Link Port DMA Channels                             | 9-4  |

| Link Port Booting                                  | 9-5  |

| Setting Link Port Modes                            | 9-5  |

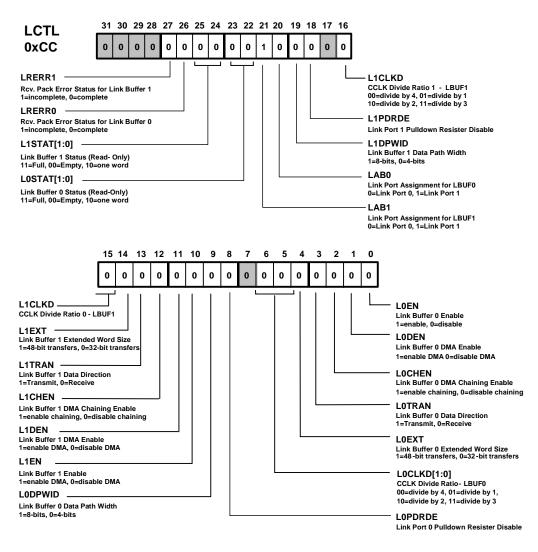

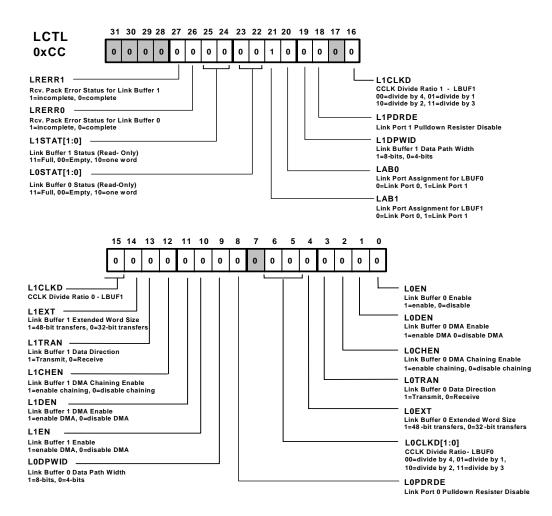

| Link Port Control Register (LCTL) Bit Descriptions | 9-7  |

| Link Data Path and Compatibility Modes             | 9-9  |

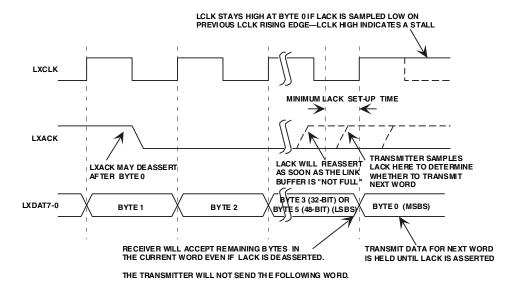

| Using Link Port Handshake Signals                  | 9-10 |

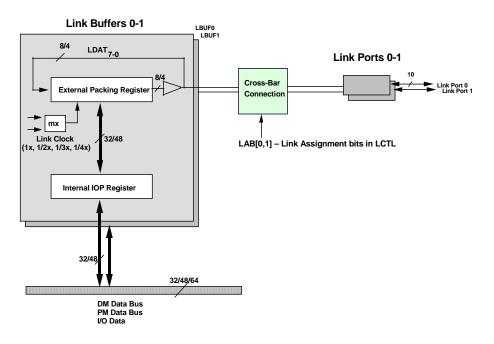

| Using Link Buffers                                 | 9-12 |

| Core Processor Access To Link Buffers              | 9-13 |

| Host Processor Access To Link Buffers              | 9-14 |

| Using Link Port DMA                                | 9-16 |

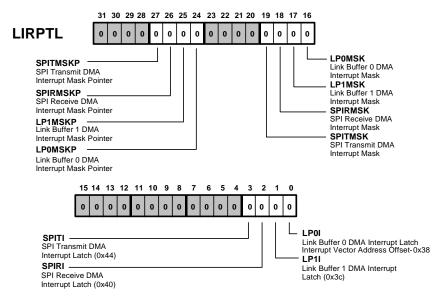

| Using Link Port Interrupts                         | 9-17 |

| Link Port Interrupts With DMA Enabled              | 9-18 |

| Link Port Interrupts With DMA Disabled             | 9-19 |

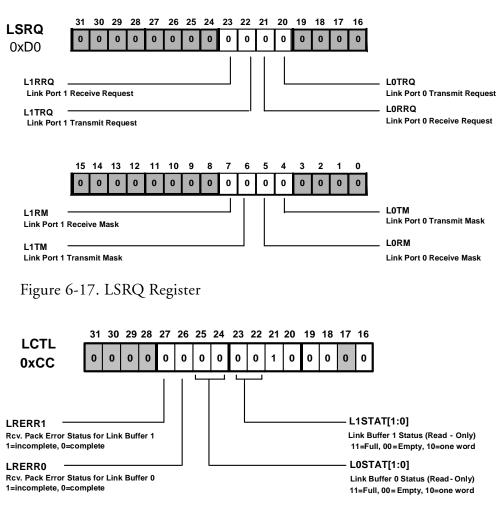

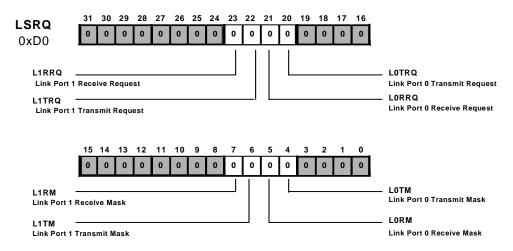

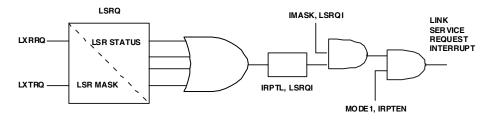

| Link Port Service Request Interrupts (LSRQ)        | 9-19 |

| Detecting Errors on Link Transmissions             | 9-22 |

| Link Port Programming Examples            | 9-23 |

|-------------------------------------------|------|

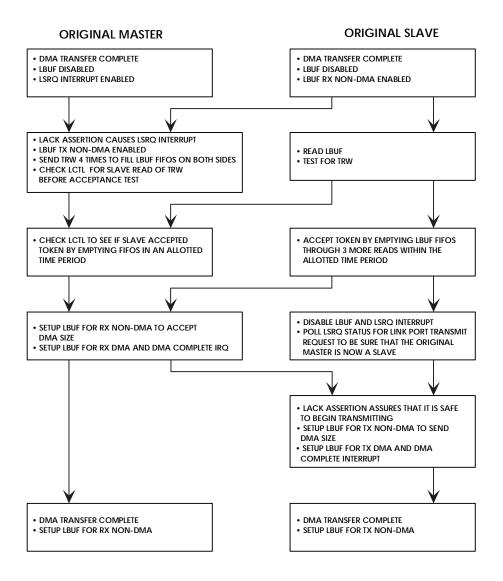

| Using Token Passing With Link Ports       | 9-27 |

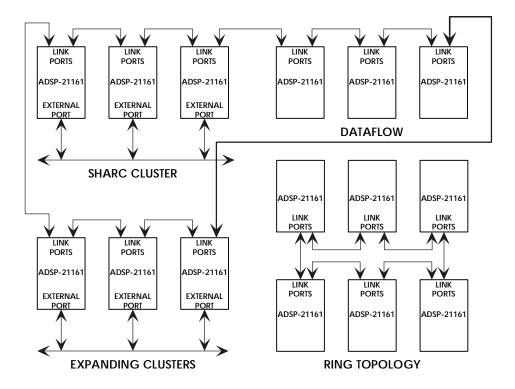

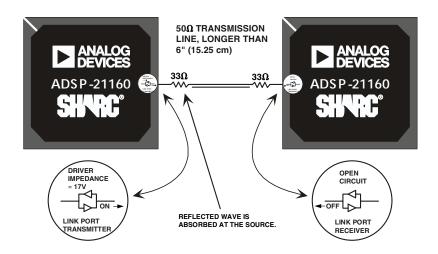

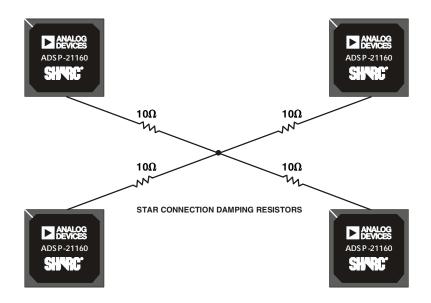

| Designing Link Port Systems               | 9-30 |

| Terminations for Link Transmission Lines  | 9-30 |

| Peripheral I/O Using Link Ports           | 9-31 |

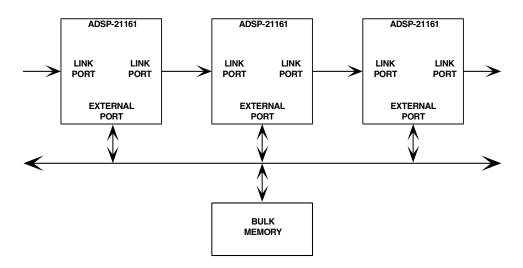

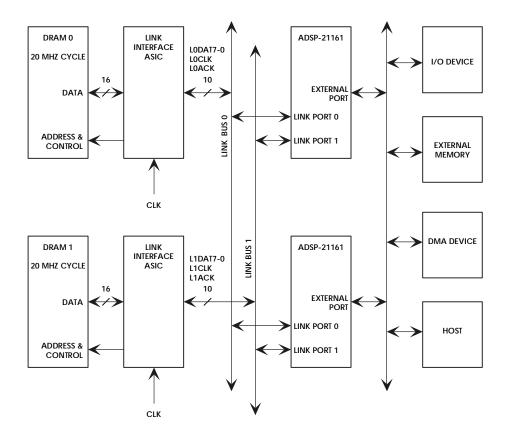

| Data Flow Multiprocessing With Link Ports | 9-33 |

## **SERIAL PORTS**

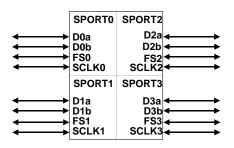

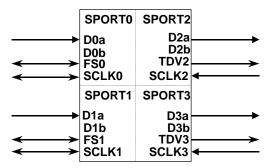

| Serial Port Pins 10-3                         |

|-----------------------------------------------|

| SPORT Interrupts 10-7                         |

| SPORT Reset 10-8                              |

| SPORT Control Registers and Data Buffers 10-9 |

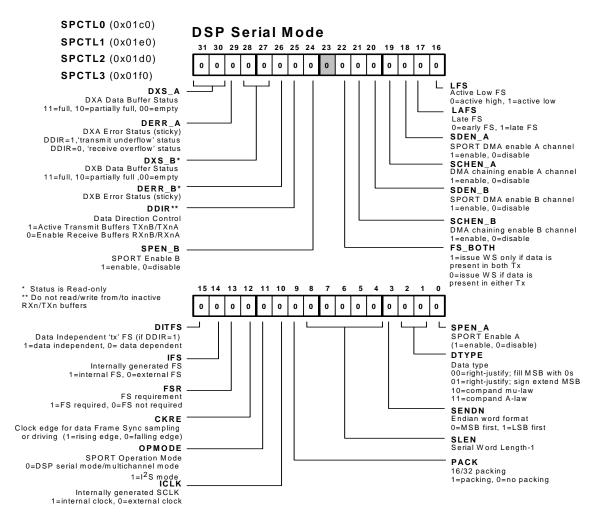

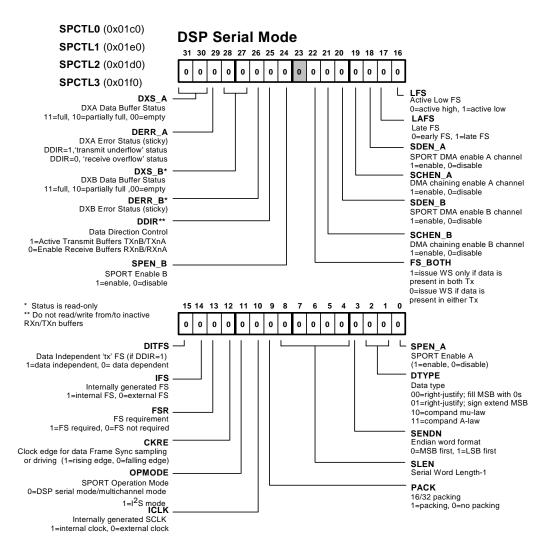

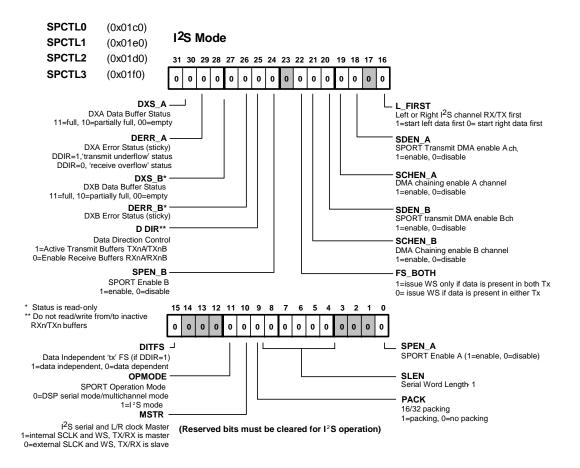

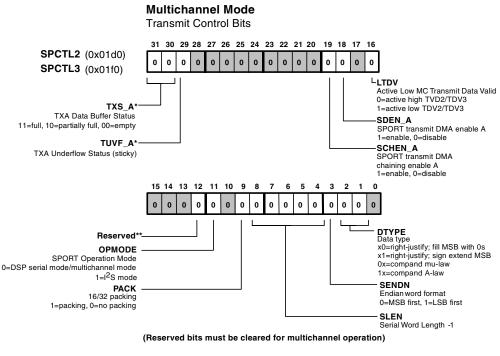

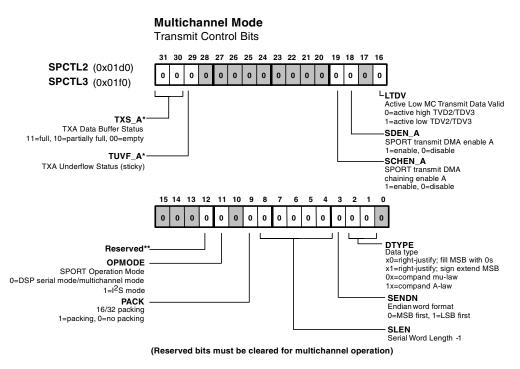

| Serial Port Control Registers (SPCTLx) 10-14  |

| Register Writes and Effect Latency 10-30      |

| Transmit and Receive Data Buffers 10-30       |

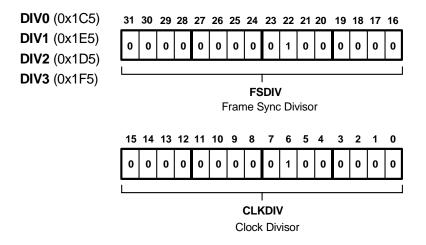

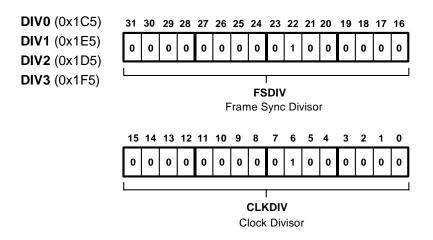

| Clock and Frame Sync Frequencies (DIV) 10-33  |

| Data Word Formats 10-35                       |

| Word Length 10-36                             |

| Endian Format 10-36                           |

| Data Packing and Unpacking 10-37              |

| Data Type 10-37                               |

| Companding 10-39                              |

| Clock Signal Options 10-40                    |

| Frame Sync Options 10-41                      |

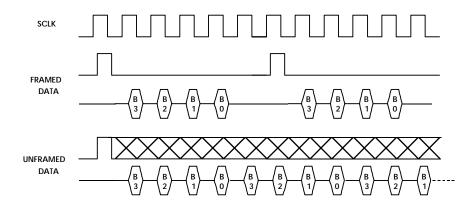

| Framed Versus Unframed 10-41                  |

| Internal Versus External Frame Syncs               | 10-42 |

|----------------------------------------------------|-------|

| Active Low Versus Active High Frame Syncs          | 10-43 |

| Sampling Edge for Data and Frame Syncs             | 10-43 |

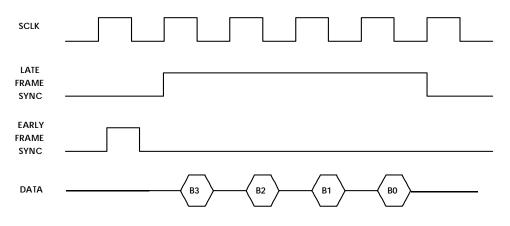

| Early Versus Late Frame Syncs                      | 10-44 |

| Data-Independent Transmit Frame Sync               | 10-45 |

| SPORT Loopback                                     | 10-46 |

| SPORT Operation Modes                              | 10-47 |

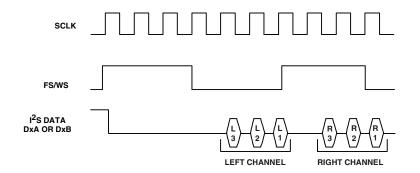

| I2S Mode                                           | 10-48 |

| Setting Internal Serial Clock and Frame Sync Rates | 10-49 |

| I2S Control Bits                                   | 10-49 |

| Setting Word Length (SLEN)                         | 10-49 |

| Selecting Transmit Receive Channel Order (L_FIRST) | 10-49 |

| Selecting the Frame Sync Options (FS_BOTH)         | 10-50 |

| Enabling SPORT Master Mode (MSTR)                  | 10-50 |

| Enabling SPORT DMA (SDEN)                          | 10-51 |

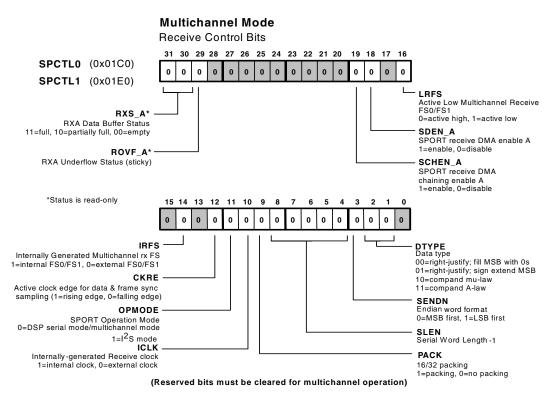

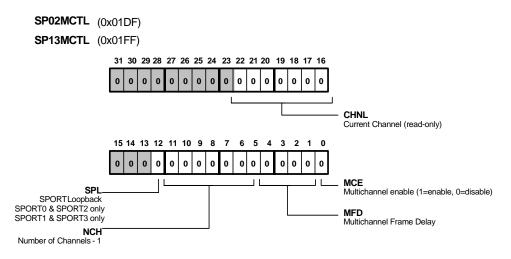

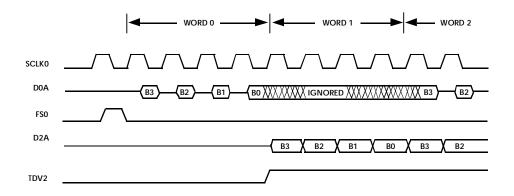

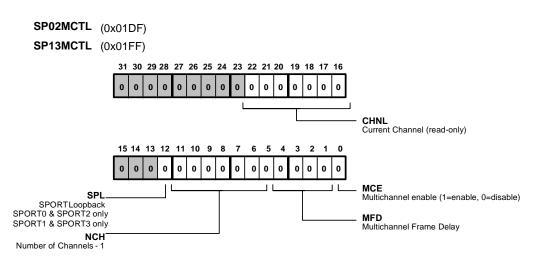

| Multichannel Operation                             | 10-52 |

| Frame Syncs in Multichannel Mode                   | 10-54 |

| Multichannel Control Bits in SPCTL                 | 10-55 |

| Channel Selection Registers                        | 10-57 |

| Transferring Data to Memory                        | 10-58 |

| DMA Block Transfers                                | 10-59 |

| Setting Up DMA on SPORT Channels                   | 10-60 |

| SPORT DMA Parameter Registers                      | 10-61 |

| SPORT DMA Chaining                                 | 10-65 |

| Single-Word Transfers       | 10-65 |

|-----------------------------|-------|

| SPORT Pin/Line Terminations | 10-66 |

| SPORT Programming Examples  | 10-67 |

## SERIAL PERIPHERAL INTERFACE (SPI)

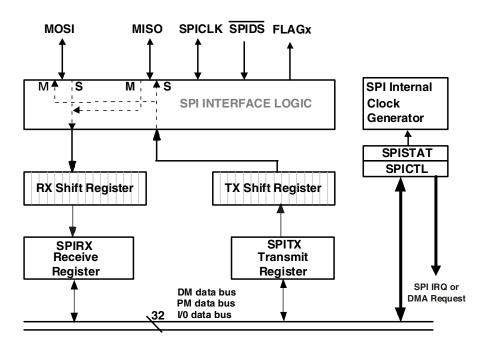

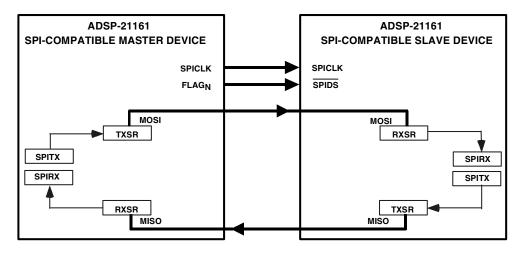

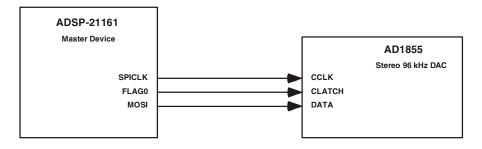

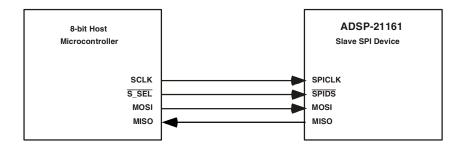

| Functional Description 11-2                                                                                                                                                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SPI Interface Signals 11-3                                                                                                                                                           |

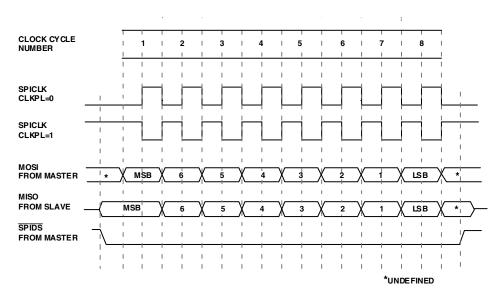

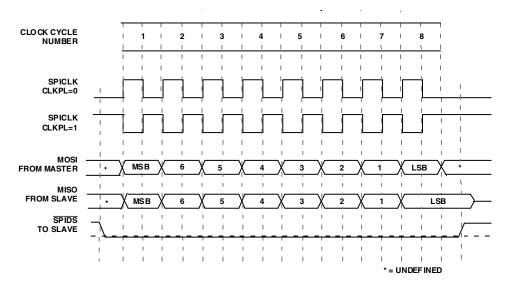

| SPICLK 11-3                                                                                                                                                                          |

| SPIDS 11-4                                                                                                                                                                           |

| FLAG 11-5                                                                                                                                                                            |

| MOSI 11-6                                                                                                                                                                            |

| MISO 11-6                                                                                                                                                                            |

| SPI Interrupts 11-8                                                                                                                                                                  |

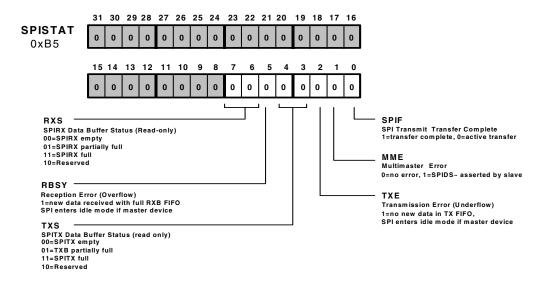

| SPI IOP Registers 11-9                                                                                                                                                               |

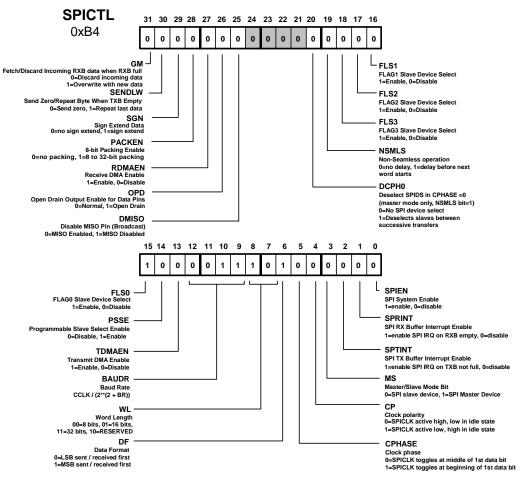

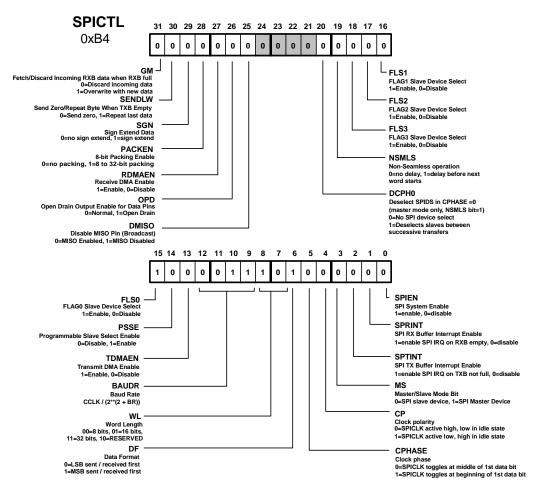

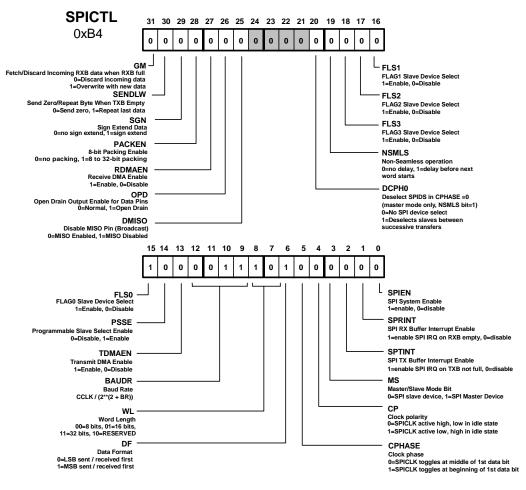

| SPI Control Register (SPICTL) 11-9                                                                                                                                                   |

|                                                                                                                                                                                      |

| Baud Rate Example 11-14                                                                                                                                                              |

| Baud Rate Example 11-14<br>Seamless Operation 11-15                                                                                                                                  |

|                                                                                                                                                                                      |

| Seamless Operation 11-15                                                                                                                                                             |

| Seamless Operation                                                                                                                                                                   |

| Seamless Operation                                                                                                                                                                   |

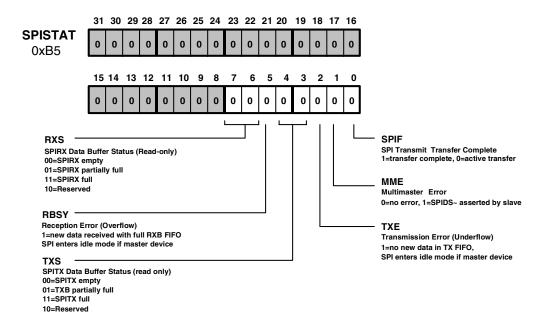

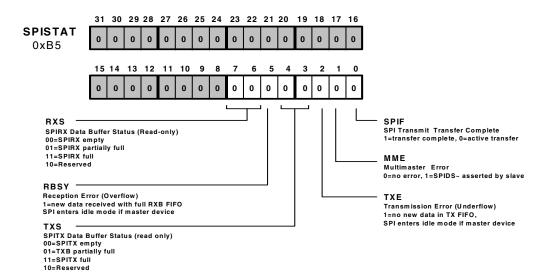

| Seamless Operation11-15SPI Status Register (SPISTAT)11-15SPI Transmit Data Buffer (SPITX)11-20SPI Receive Data Buffer (SPIRX)11-20                                                   |

| Seamless Operation11-15SPI Status Register (SPISTAT)11-15SPI Transmit Data Buffer (SPITX)11-20SPI Receive Data Buffer (SPIRX)11-20SPI Shift Registers11-21                           |

| Seamless Operation11-15SPI Status Register (SPISTAT)11-15SPI Transmit Data Buffer (SPITX)11-20SPI Receive Data Buffer (SPIRX)11-20SPI Shift Registers11-21SPI Data Word Formats11-21 |

| Interrupt and DMA Driven Transfers | 11-26  |

|------------------------------------|--------|

| Core Driven Transfers              | 11-26  |

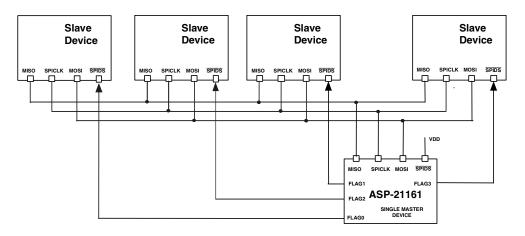

| Automatic Slave Selection          | 11-26  |

| User Controlled Slave Selection    | 11-27  |

| Slave Mode Operation               | 11-28  |

| Error Signals and Flags            | 11-29  |

| Multi-Master Error (MME)           | 11-30  |

| Transmission Error (TXE)           | 11-30  |

| Reception Error (RBSY)             | 11-31  |

| SPI/Link Port DMA                  | 11-32  |

| DMA Operation in SPI Master Mode   | 11-32  |

| DMA Operation in Slave Mode        | 11-33  |

| SPI Booting                        | 11-34  |

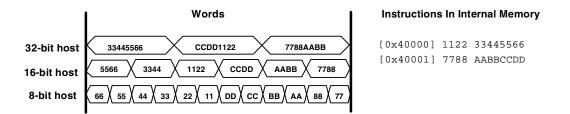

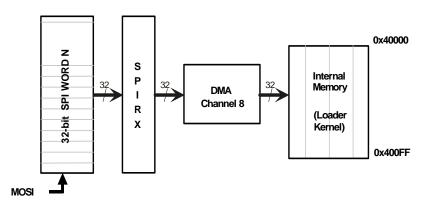

| 32-Bit SPI Host Boot               | 11-38  |

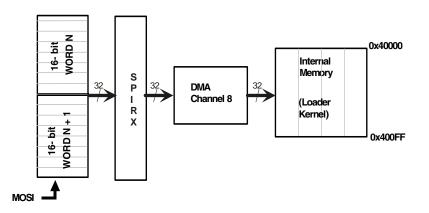

| 16-Bit SPI Host Boot               | 11-39  |

| 8-Bit SPI Host Boot                | 11-41  |

| Multiprocessor SPI Port Booting    | 11-42  |

| SPI Programming Example            | 11-44  |

| JTAG TEST-EMULATION PORT           |        |

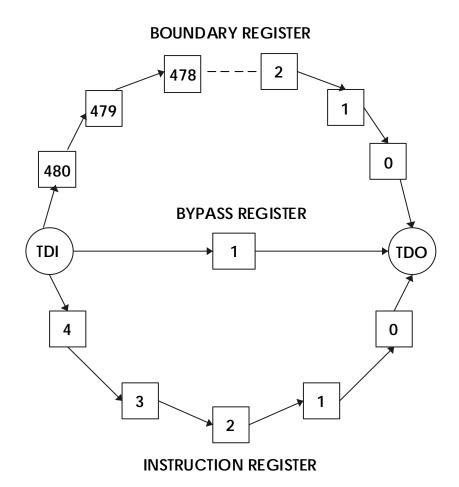

| JTAG Test Access Port              | . 12-3 |

| Instruction Register               | . 12-4 |

| EMUPMD Shift Register              | . 12-5 |

| EMUPX Shift Register               | . 12-6 |

| EMUPC Shift Register 12-7                           |

|-----------------------------------------------------|

| EMUCTL Shift Register 12-8                          |

| EMUSTAT Shift Register 12-11                        |

| BRKSTAT Shift Register 12-12                        |

| MEMTST Shift Register 12-13                         |

| PSx, DMx, IOx, and EPx (Breakpoint) Registers 12-13 |

| EMUN Register 12-16                                 |

| EMUCLK and EMUCLK2 Registers 12-16                  |

| EMUIDLE Instruction 12-17                           |

| In Circuit Signal Analyzer (ICSA) Function 12-17    |

| Boundary Register 12-17                             |

| Device Identification Register 12-28                |

| Built-In Self-Test Operation (BIST) 12-28           |

| Private Instructions 12-28                          |

| References 12-29                                    |

|                                                     |

## SYSTEM DESIGN

| Pin | Descriptions                    | 13-2  |

|-----|---------------------------------|-------|

|     | Input Synchronization Delay     | 13-18 |

|     | Pin States At Reset             | 13-19 |

|     | Pull-Up and Pull-Down Resistors | 13-22 |

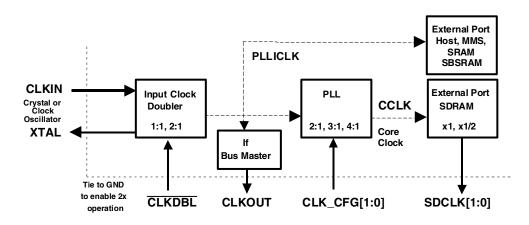

|     | Clock Derivation                | 13-24 |

|     | Timing Specifications           | 13-25 |

|     | RESET and CLKIN                 | 13-28 |

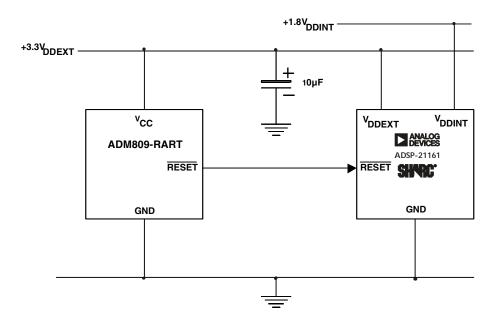

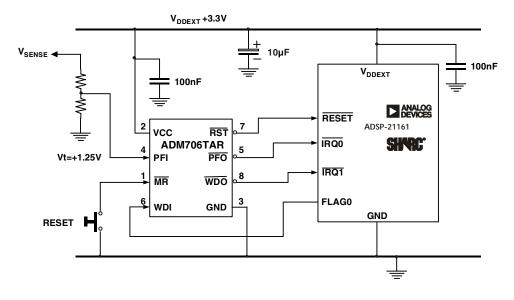

|     | Reset Generators                | 13-31 |

|     |                                 |       |

| Interrupt and Timer Pins                     | 13-33 |

|----------------------------------------------|-------|

| Core-Based Flag Pins                         | 13-34 |

| Flag Inputs                                  | 13-34 |

| Flag Outputs                                 | 13-34 |

| Programmable I/O Flags                       | 13-35 |

| Example #1: Configuring FLGx as Output Flags | 13-37 |

| Example #2: Configuring FLGx as Input Flags  | 13-38 |

| System Design Considerations for Flags       | 13-38 |

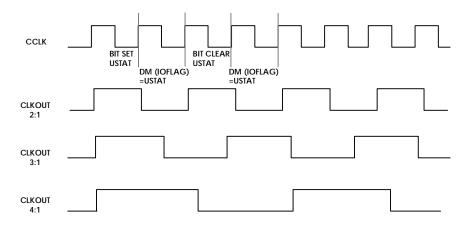

| Example #3: Programming 2:1 Clock Ratio      | 13-40 |

| Example #4: Programming 3:1 Clock Ratio      | 13-40 |

| Example #5: Programming 4:1 Clock Ratio      | 13-40 |

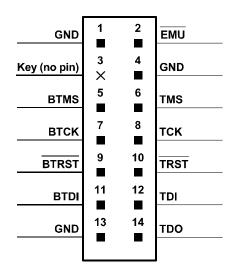

| JTAG Interface Pins                          | 13-41 |

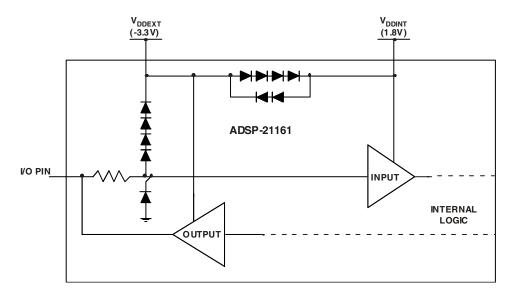

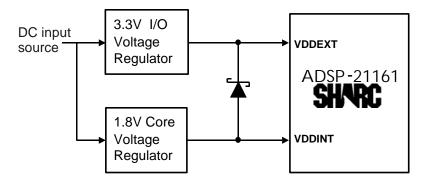

| Dual-Voltage Power-up Sequencing             | 13-41 |

| PLL Start-Up (Revisions 1.0/1.1)             | 13-44 |

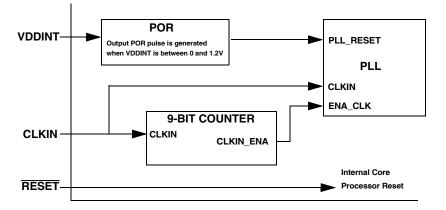

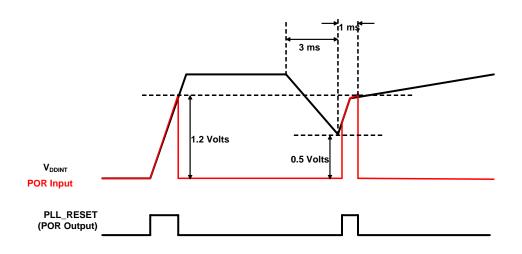

| Power On Reset (POR) Circuit                 | 13-44 |

| PLL CLKIN Enable Circuit                     | 13-46 |

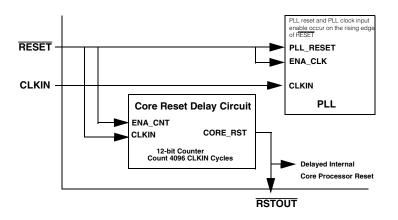

| PLL Start-Up (Revision 1.2)                  | 13-48 |

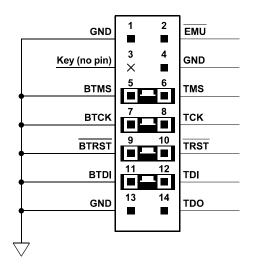

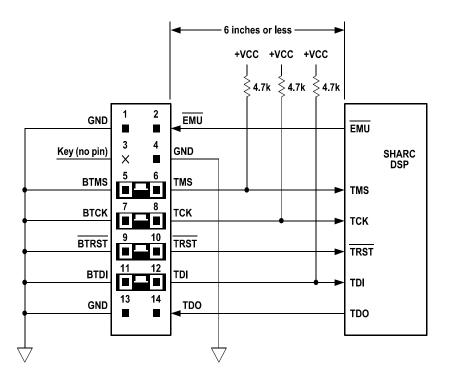

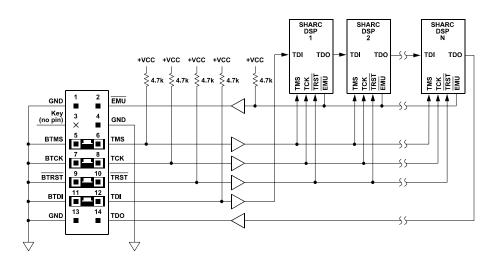

| Designing For JTAG Emulation                 | 13-49 |

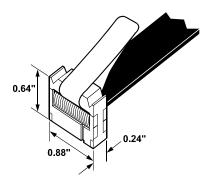

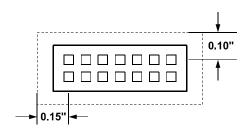

| Target Board Connector                       | 13-50 |

| Layout Requirements                          | 13-54 |

| Power Sequence for Emulation                 | 13-56 |

| Additional JTAG Emulator References          | 13-56 |

| Pod Specifications                           | 13-56 |

| JTAG Pod Connector                           | 13-57 |

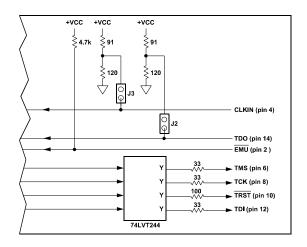

| 3.3 V Pod Logic 1                             | 13-58          |

|-----------------------------------------------|----------------|

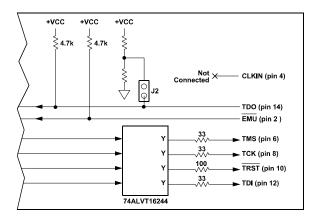

| 2.5 V Pod Logic 1                             | 13-59          |

| Conditioning Input Signals 1                  | 13-60          |

| Link Port Input Filter Circuits 1             | 13-60          |

| RESET Input Hysteresis 1                      | l <b>3-6</b> 1 |

| Designing For High Frequency Operation 1      | 13-62          |

| Clock Specifications and Jitter 1             | 13-63          |

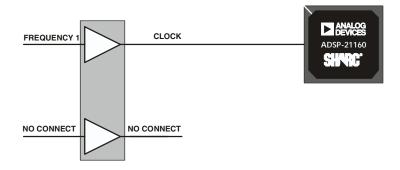

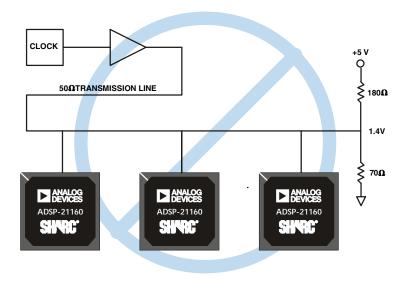

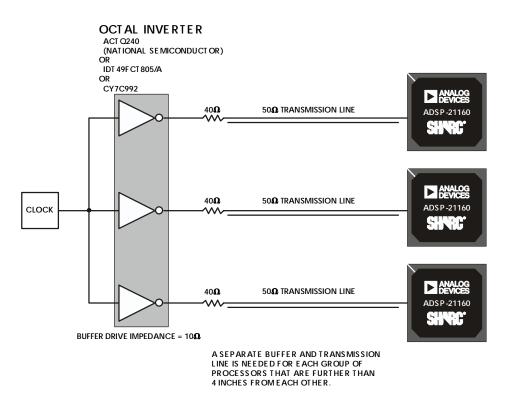

| Clock Distribution 1                          | 13-63          |

| Point-to-Point Connections 1                  | 13-65          |

| Signal Integrity 1                            | l <b>3-6</b> 7 |

| Other Recommendations and Suggestions 1       | 13-68          |

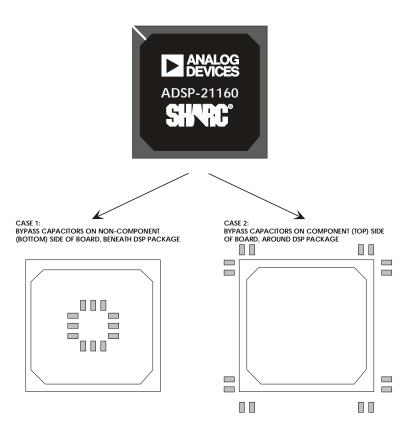

| Decoupling Capacitors and Ground Planes 1     | 13-69          |

| Oscilloscope Probes 1                         | 13-70          |

| Recommended Reading 1                         | 13-71          |

| Booting Single and Multiple Processors 1      | 13-71          |

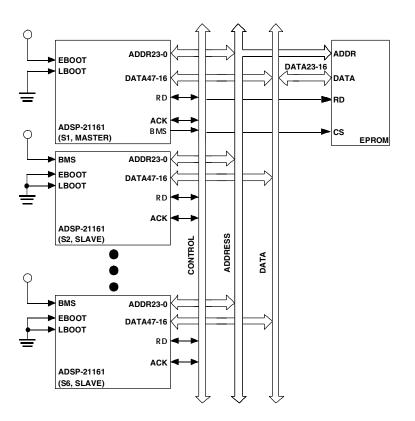

| Multiprocessor Host Booting 1                 | 13-73          |

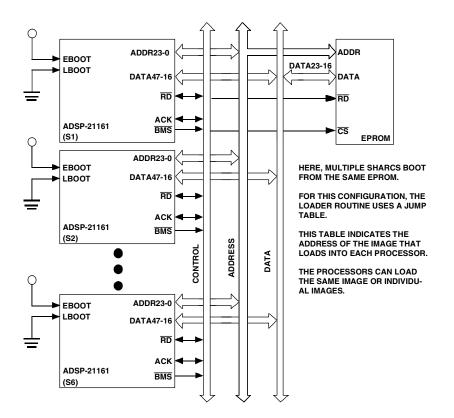

| Multiprocessor EPROM Booting 1                | 13-73          |

| Booting From a Single EPROM 1                 | 13-73          |

| Sequential Booting 1                          | 13-74          |

| Multiprocessor Link Port Booting 1            | 13-75          |

| Multiprocessor Booting From External Memory 1 | 13-75          |

| Data Delays, Latencies, and Throughput 1      | 13-76          |

| Execution Stalls 1                            | l <b>3-</b> 77 |

| DAG Stalls 1                                  | 13-77          |

| Memory Stalls                    | 13-77 |

|----------------------------------|-------|

| IOP Register Stalls              | 13-78 |

| DMA Stalls                       | 13-78 |

| Link Port and Serial Port Stalls | 13-78 |

## REGISTERS

| Control and Status System Registers               | A-2          |

|---------------------------------------------------|--------------|

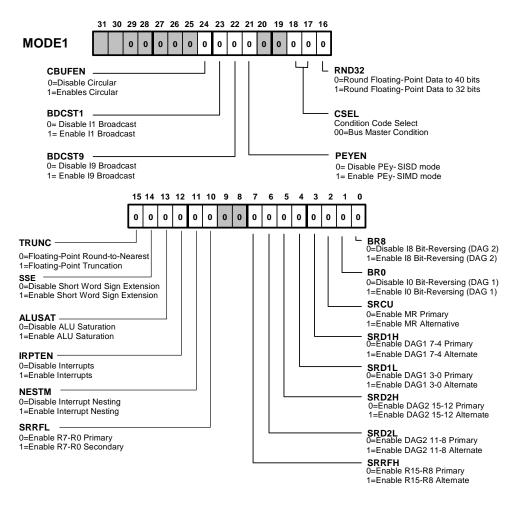

| Mode Control 1 Register (MODE1)                   | A-3          |

| Mode Mask Register (MMASK)                        | A-8          |

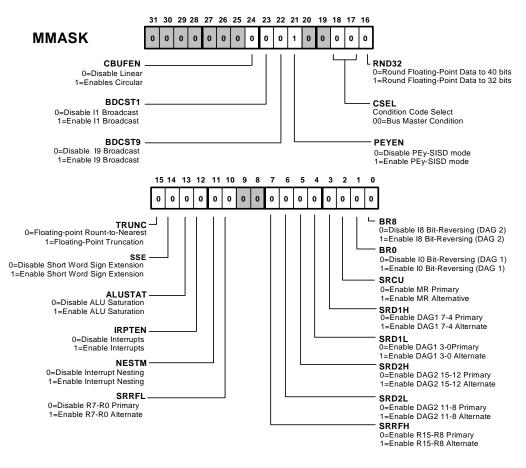

| Mode Control 2 Register (MODE2) A                 | <b>\-10</b>  |

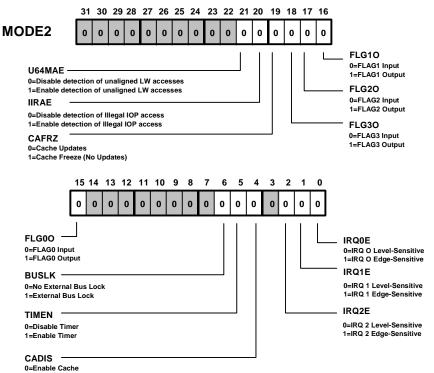

| Arithmetic Status Registers (ASTATx and ASTATy) A | A-13         |

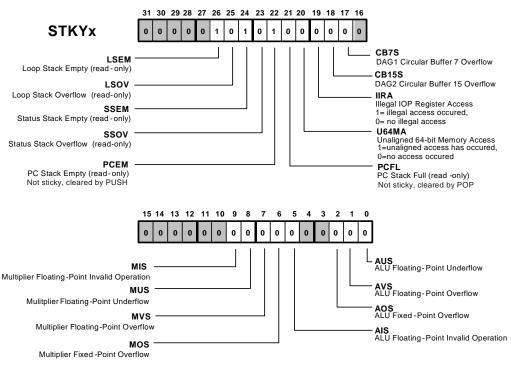

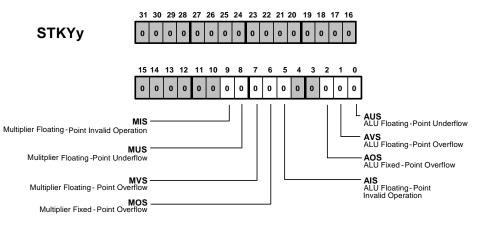

| Sticky Status Registers (STKYx and STKYy) A       | <b>\-18</b>  |

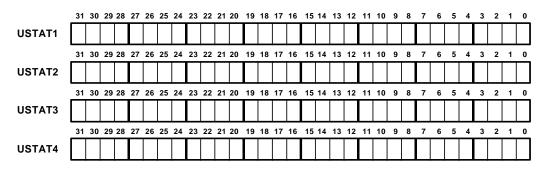

| User-Defined Status Registers (USTATx) A          | 4-22         |

| Processing Element Registers A                    | 4-23         |

| Data File Data Registers (Rx, Fx, Sx) A           | 4-23         |

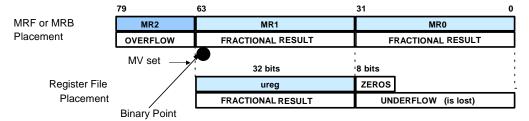

| Multiplier Results Registers (MRFx, MRBx) A       | <b>\-24</b>  |

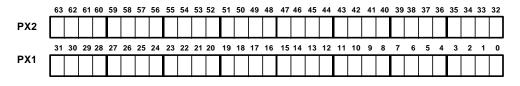

| Program Memory Bus Exchange Register (PX) A       | 4-25         |

| Program Sequencer Registers A                     | 4-25         |

| Interrupt Latch Register (IRPTL) A                | <b>\-2</b> 7 |

| Interrupt Mask Register (IMASK) A                 | 4-31         |

| Interrupt Mask Pointer Register (IMASKP) A        | 4-32         |

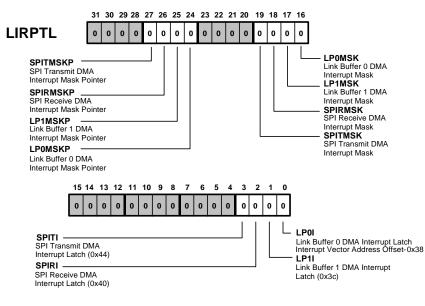

| Link Port Interrupt Register (LIRPTL) A           | 4-34         |

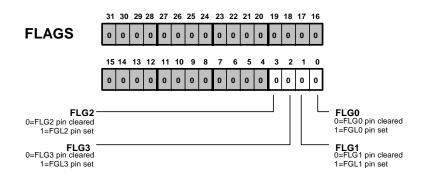

| Flag Value Register (FLAGS) A                     | 4-37         |

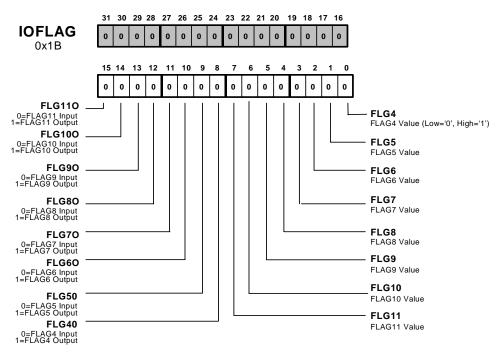

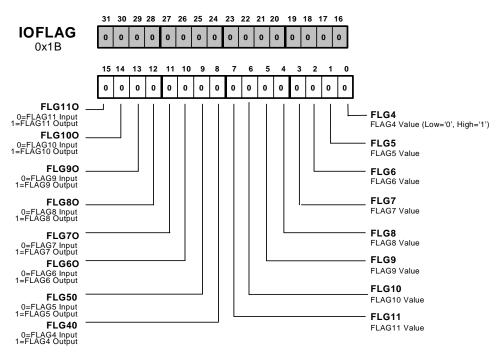

| IOFLAG Value Register A                           | 4-38         |

| Program Counter Register (PC) A                   | <b>\-4</b> 1 |

|     | Program Counter Stack Register (PCSTK)             | A-44 |

|-----|----------------------------------------------------|------|

|     | Program Counter Stack Pointer Register (PCSTKP)    | A-44 |

|     | Fetch Address Register (FADDR)                     | A-44 |

|     | Decode Address Register (DADDR)                    | A-44 |

|     | Loop Address Stack Register (LADDR)                | A-45 |

|     | Current Loop Counter Register (CURLCNTR)           | A-45 |

|     | Loop Counter Register (LCNTR)                      | A-45 |

|     | Timer Period Register (TPERIOD)                    | A-46 |

|     | Timer Count Register (TCOUNT)                      | A-46 |

| Da  | ta Address Generator Registers                     | A-46 |

|     | Index Registers (Ix)                               | A-47 |

|     | Modify Registers (Mx)                              | A-47 |

|     | Length and Base Registers (Lx,Bx)                  | A-47 |

| I/C | O Processor Registers                              | A-47 |

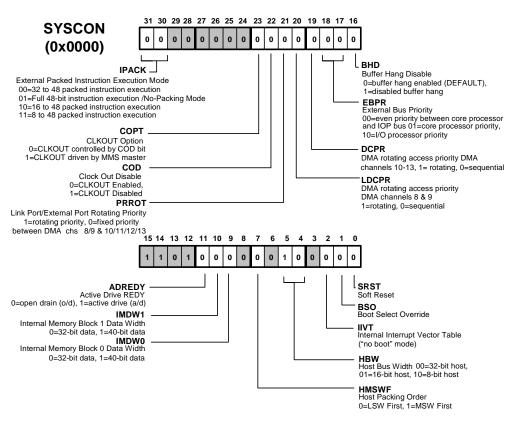

|     | System Configuration Register (SYSCON)             | A-60 |

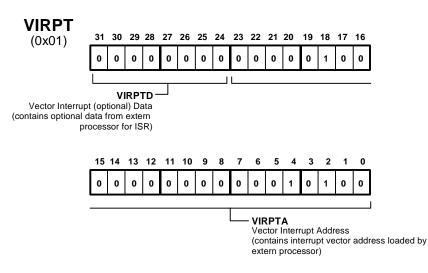

|     | Vector Interrupt Address Register (VIRPT)          | A-63 |

|     | External Memory Waitstate and Access Mode Register |      |

|     | (WAIT)                                             |      |

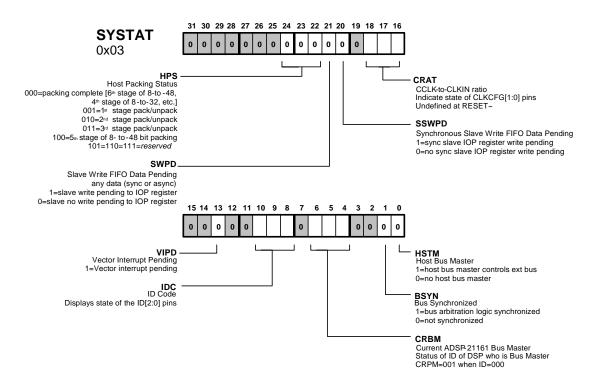

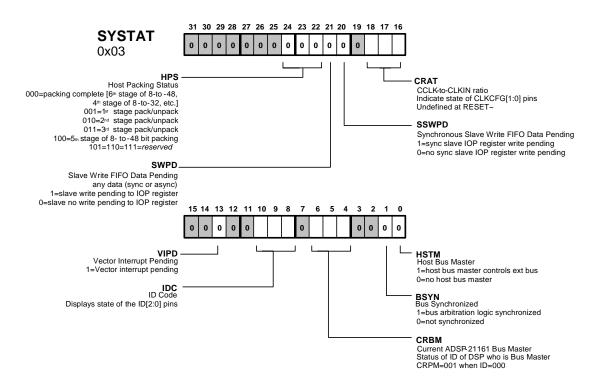

|     | System Status Register (SYSTAT)                    | A-69 |

|     | SDRDIV Register (SDRDIV)                           | A-72 |

|     | SDRAM Control Register (SDCTL)                     | A-73 |

|     | External Port DMA Buffer Registers (EPBx)          | A-76 |

|     | Message Registers (MSGRx)                          | A-77 |

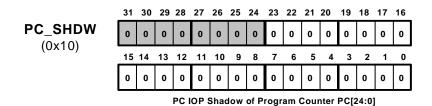

|     | PC Shadow Register (PC_SHDW)                       | A-77 |

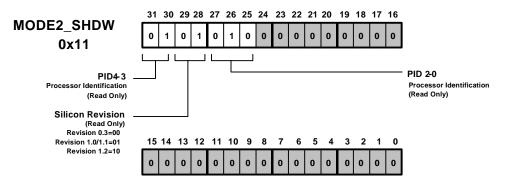

|     | MODE2 Shadow Register (MODE2_SHDW)                 | A-78 |

|     |                                                    |      |

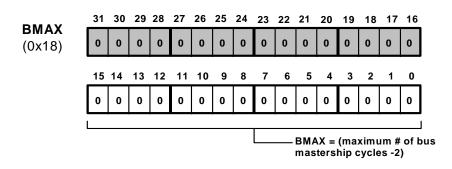

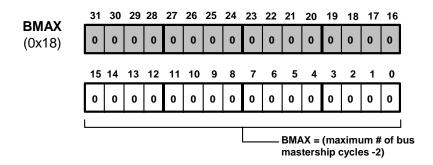

| Bus Time-Out Maximum Register (BMAX)              | A-79  |

|---------------------------------------------------|-------|

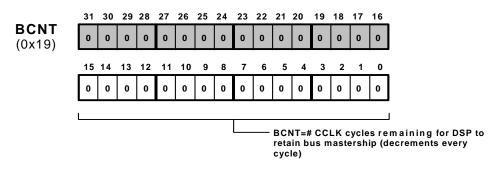

| Bus (Time-Out) Counter Register (BCNT)            | A-79  |

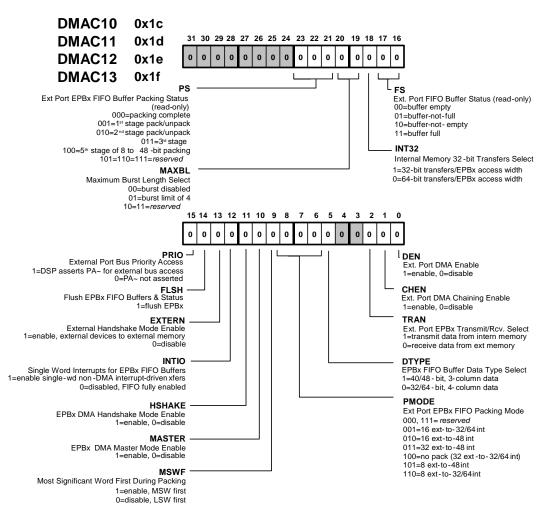

| External Port DMA Control Registers (DMACx)       | A-80  |

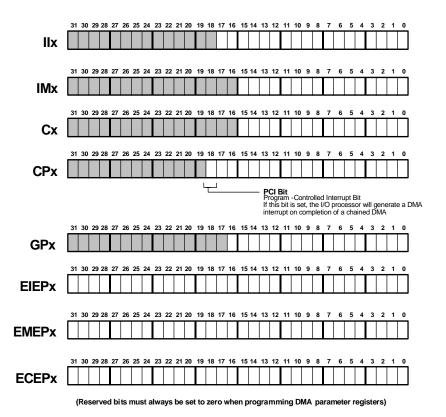

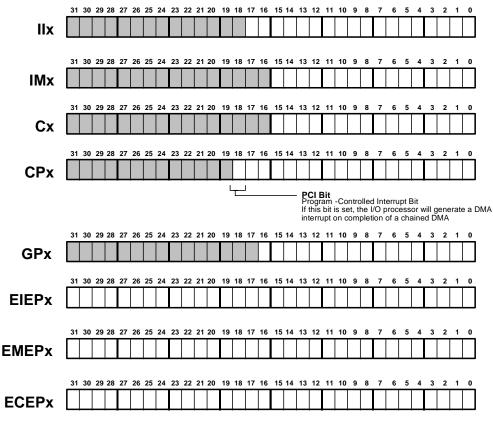

| Internal Memory DMA Index Registers (IIx)         | A-87  |

| Internal Memory DMA Modifier Registers (IMx)      | A-87  |

| Internal Memory DMA Count Registers (Cx)          | A-87  |

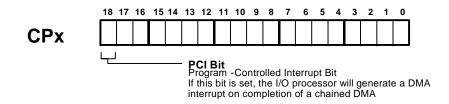

| Chain Pointer For Next DMA TCB Registers (CPx)    | A-88  |

| General Purpose DMA Registers (GPx)               | A-89  |

| External Memory DMA Index Registers (EIEPx)       | A-89  |

| External Memory DMA Modifier Registers (EMEPx)    | A-89  |

| External Memory DMA Count Registers (ECEPx)       | A-90  |

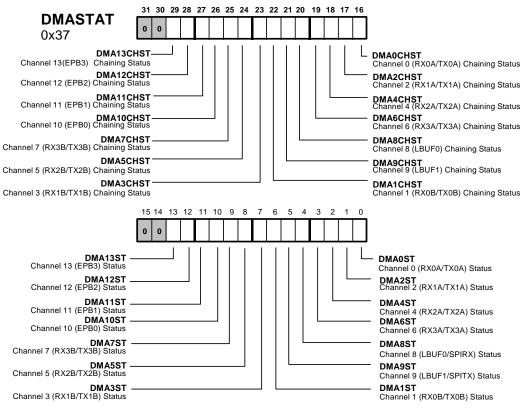

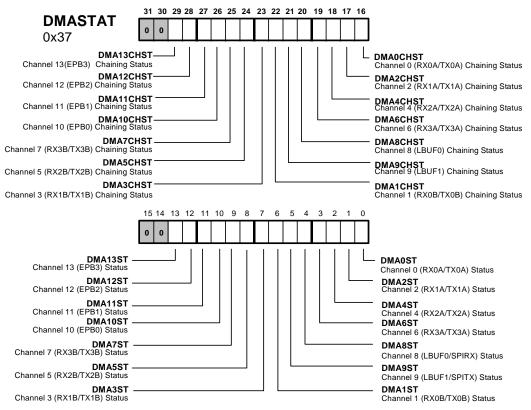

| DMA Channel Status Register (DMASTAT)             | A-90  |

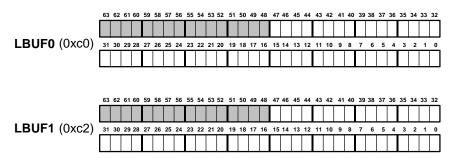

| Link Port Buffer Registers (LBUFx)                | A-92  |

| Link Port Buffer Control Register (LCTL)          | A-92  |

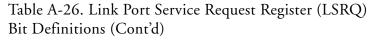

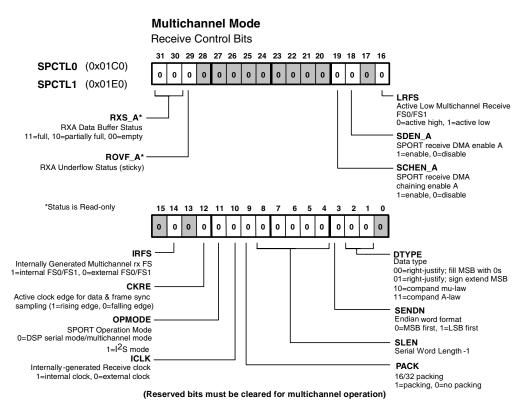

| Link Port Service Request & Mask Register (LSRQ)  | A-98  |

| Serial Port Registers                             | A-100 |

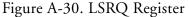

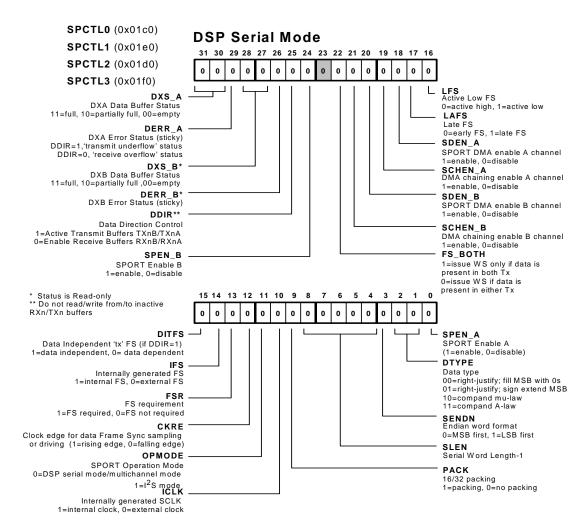

| SPORT Serial Control Registers (SPCTLx)           | A-100 |

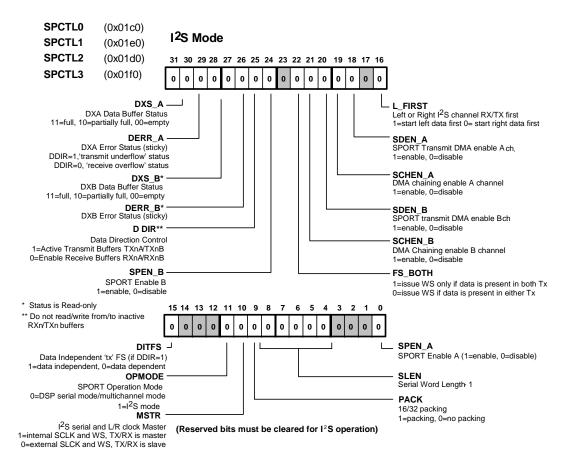

| SPORT Multichannel Control Registers (SPxyMCTL) . | A-109 |

| SPORT Transmit Buffer Registers (TXx)             | A-111 |

| SPORT Receive Buffer Registers (RXx)              | A-111 |

| SPORT Divisor Registers (DIVx)                    | A-112 |

| SPORT Count Registers (CNTx)                      | A-113 |

| SPORT Transmit Select Registers (MT2CSx and       |       |

| MT3CSx)                                           | A-113 |

| SPORT Transmit Compand Registers (MT2CCSx and MT3CCSx) | A-113 |

|--------------------------------------------------------|-------|

|                                                        |       |

| SPORT Receive Select Registers                         | A-114 |

| SPORT Receive Compand Registers                        | A-114 |

| Serial Peripheral Interface Registers                  | A-114 |

| SPI Port Status Register                               | A-115 |

| SPI Control Register (SPICTL)                          | A-117 |

| SPI Receive Buffer Register (SPIRX)                    | A-120 |

| SPI Transmit Buffer Register (SPITX)                   | A-121 |

| Register and Bit #Defines (def21161.h)                 | A-121 |

|                                                        |       |

## **INTERRUPT VECTOR ADDRESSES**

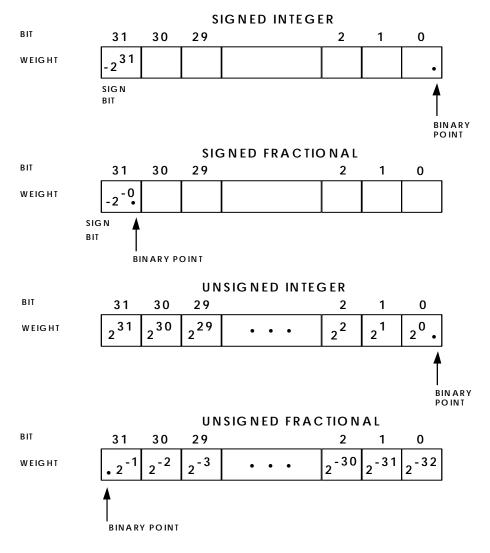

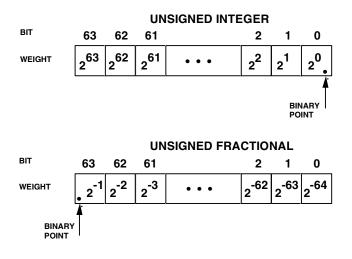

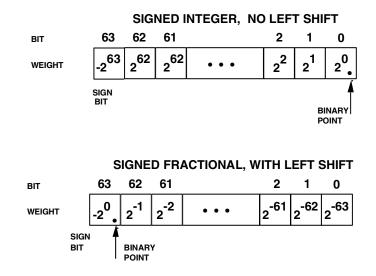

### NUMERIC FORMATS

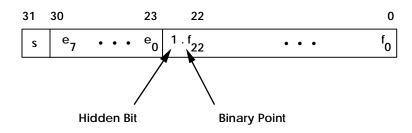

| IEEE Single-Precision Floating-Point Data | C-1 |

|-------------------------------------------|-----|

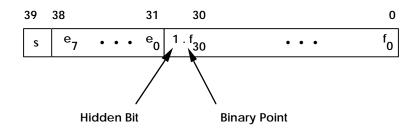

| Extended-Precision Floating-Point         | C-3 |

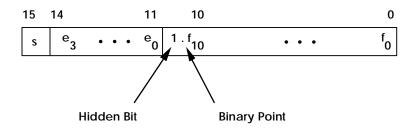

| Short Word Floating-Point Format          | C-4 |

| Packing for Floating-Point Data           | C-4 |

| Fixed-Point Formats                       | C-6 |

## GLOSSARY

### INDEX

# **1 INTRODUCTION**

Thank you for purchasing the Analog Devices SHARC® digital signal processor (DSP).

## **Design Advantages**

The ADSP-21161 processor is a high-performance 32-bit processor used for medical imaging, communications, military, audio, test equipment, 3D graphics, speech recognition, motor control, imaging, and other applications. This processor builds on the ADSP-21000 Family processor core to form a complete system-on-a-chip, adding a dual-ported on-chip SRAM, integrated I/O peripherals, and an additional processing element for Single-Instruction-Multiple-Data (SIMD) support.

The SHARC architecture balances a high performance processor core with high performance buses (PM, DM, IO). In the core, every instruction can execute in a single cycle. The buses and instruction cache provide rapid, unimpeded data flow to the core to maintain the execution rate.

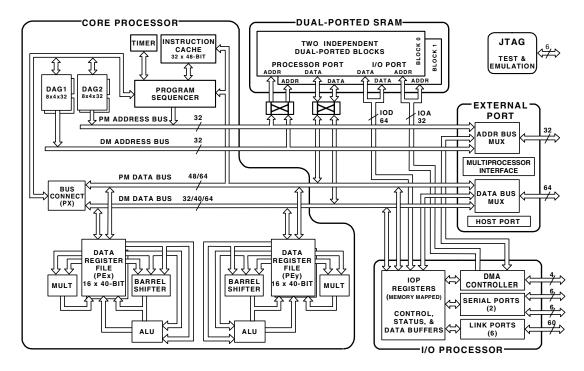

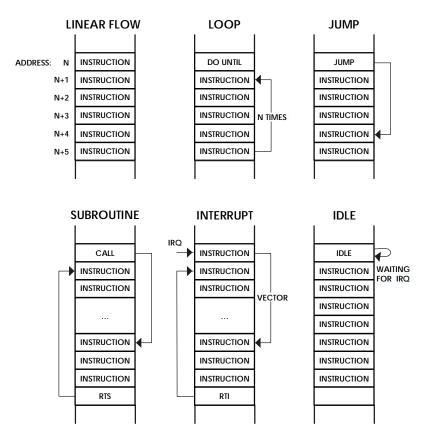

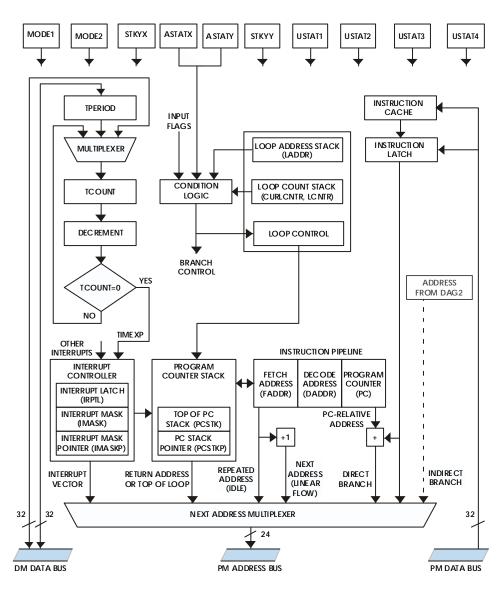

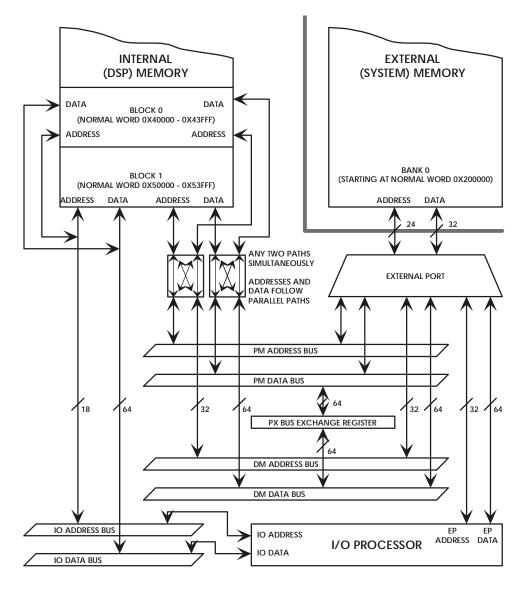

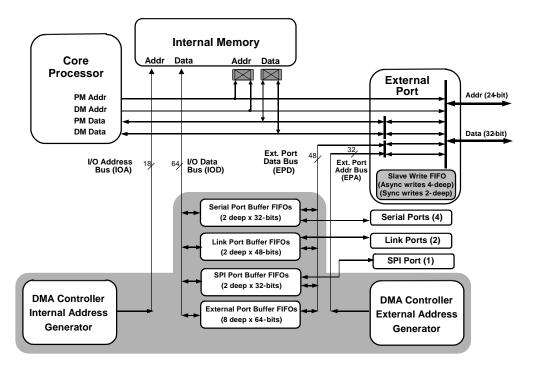

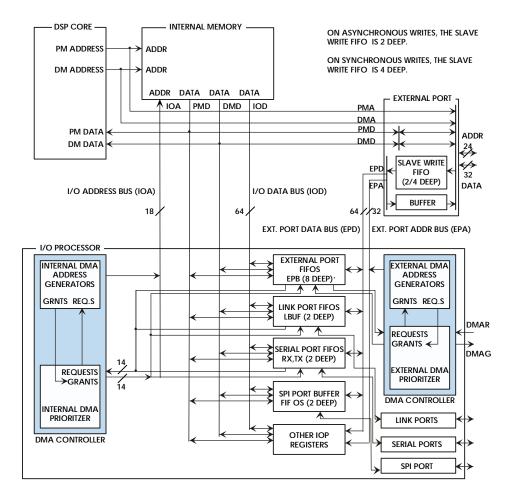

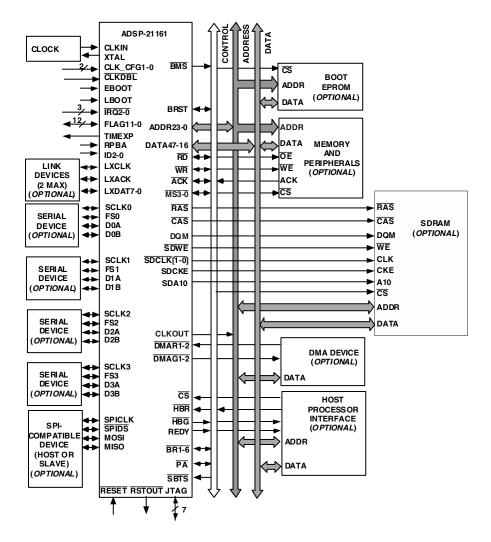

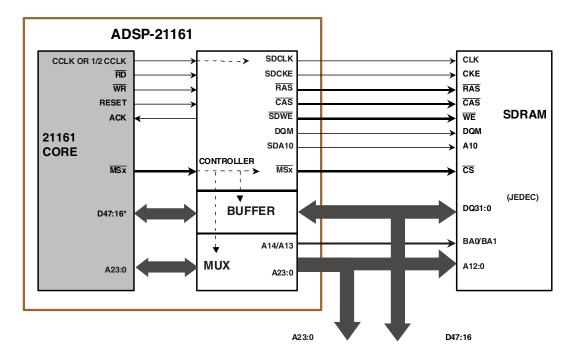

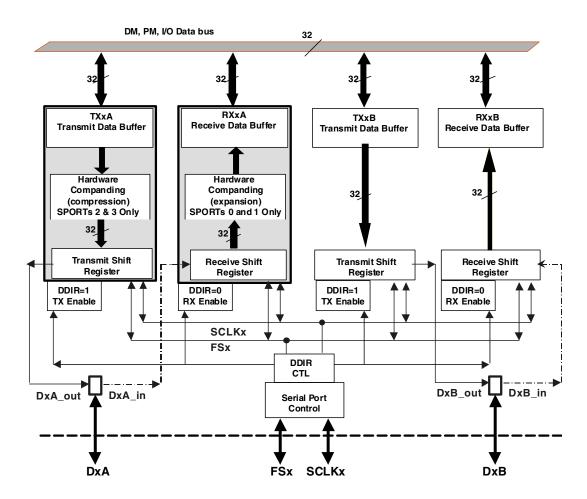

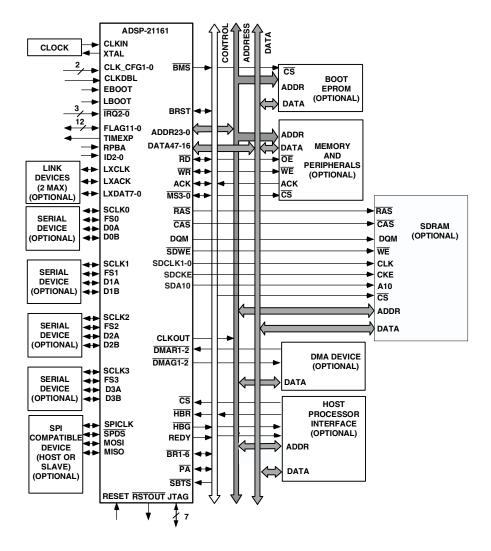

Figure 1-1 shows a detailed block diagram of the processor, which illustrates the following architectural features.

- Two processing elements (PEx and PEy), each containing 32-Bit IEEE floating-point computation unit—multiplier, ALU, Shifter, and data register file

- Program sequencer with related instruction cache, interval timer, and Data Address Generators (DAG1 and DAG2)

- Dual-ported SRAM

- External port for interfacing to off-chip memory such as SDRAM, peripherals, hosts, and multiprocessor systems

- Input/Output (IO) processor with integrated DMA controller, SPI-compatible port, serial ports, and link ports for point-to-point multiprocessor communications

- JTAG Test Access Port for emulation

Figure 1-1. ADSP-21161 SHARC Block Diagram

Figure 1-1 also shows the three on-chip buses of the ADSP-21161 processor: the Program Memory (PM) bus, Data Memory (DM) bus, and Input/Output (IO) bus. The PM bus provides access to either instructions

or data. During a single cycle, these buses let the processor access two data operands from memory, access an instruction (from the cache), and perform a DMA transfer.

The buses connect to the ADSP-21161 processor external port, which provides the processor interface to external memory, memory-mapped I/O, a host processor, and additional multiprocessing ADSP-21161 processors. The external port performs bus arbitration and supplies control signals to shared, global memory and I/O devices.

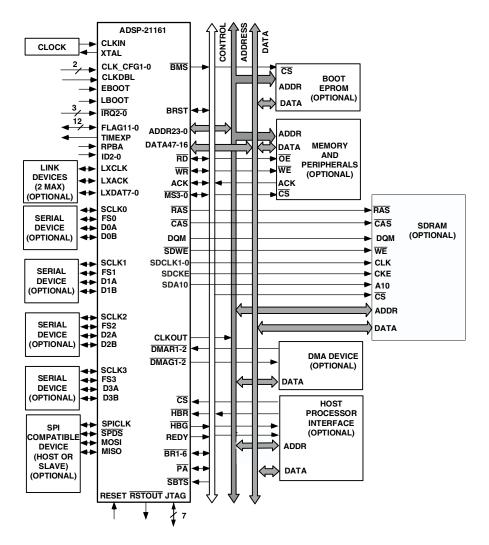

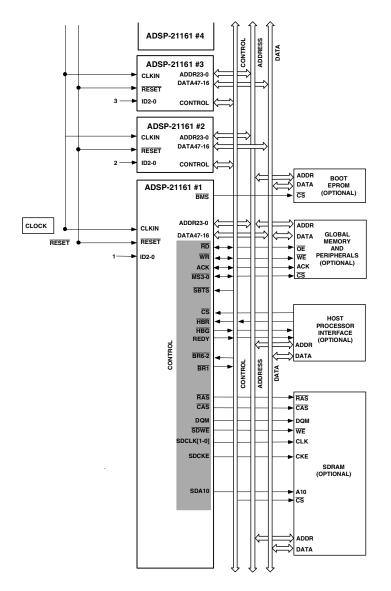

Figure 1-2 illustrates a typical single-processor system.

The ADSP-21161 processor includes extensive support for multiprocessor systems as well. For more information, see "Multiprocessor (MP) Interface" on page 7-87.

Further, the ADSP-21161 processor addresses the five central requirements for DSPs:

- Fast, flexible arithmetic computation units

- Unconstrained data flow to and from the computation units

- Extended precision and dynamic range in the computation units

- Dual address generators with circular buffering support

- Efficient program sequencing

Fast, Flexible Arithmetic. The ADSP-21000 Family processors execute all instructions in a single cycle. They provide fast cycle times and a complete set of arithmetic operations. The processor is IEEE floating-point compatible and allows either interrupt on arithmetic exception or latched status exception handling.

Unconstrained Data Flow. The ADSP-21161 processor has a Super Harvard Architecture combined with a 10-port data register file. In every cycle, the processor can write or read two operands to or from the register

Figure 1-2. Typical Single Processor System

file, supply two operands to the ALU, supply two operands to the multiplier, and receive three results from the ALU and multiplier. The processor's 48-bit orthogonal instruction word supports parallel data transfers and arithmetic operations in the same instruction. **40-Bit Extended Precision.** The processor handles 32-bit IEEE floating-point format, 32-bit integer and fractional formats (twos-complement and unsigned), and extended-precision 40-bit floating-point format. The processors carry extended precision throughout their computation units, limiting intermediate data truncation errors.

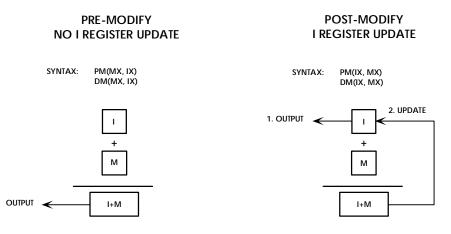

**Dual Address Generators.** The processor has two Data Address Generators (DAGs) that provide immediate or indirect (pre- and post-modify) addressing. Modulus, bit-reverse, and broadcast operations are supported with no constraints on data buffer placement.

Efficient Program Sequencing. In addition to zero-overhead loops, the processor supports single-cycle setup and exit for loops. Loops are both nestable (six levels in hardware) and interruptable. The processors support both delayed and non-delayed branches.

## Architecture Overview

The ADSP-21161 processor forms a complete system-on-a-chip, integrating a large, high-speed SRAM and I/O peripherals supported by a dedicated I/O bus. The following sections summarize the features of each functional block in the ADSP-21161 processor SHARC architecture, which appears in Figure 1-1 on page 1-2. With each summary, a cross reference points to the sections where the features are described in greater detail.

## Processor Core

The processor core of the ADSP-21161 processor consists of two processing elements (each with three computation units and data register file), a program sequencer, two data address generators, a timer, and an instruction cache. All digital signal processing occurs in the processor core.

#### **Processing Elements**

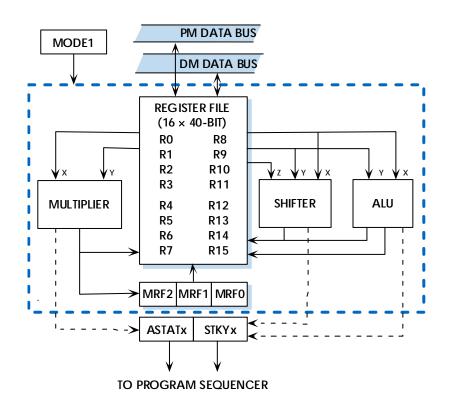

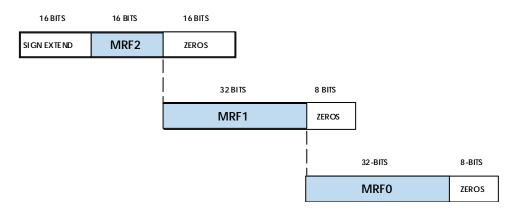

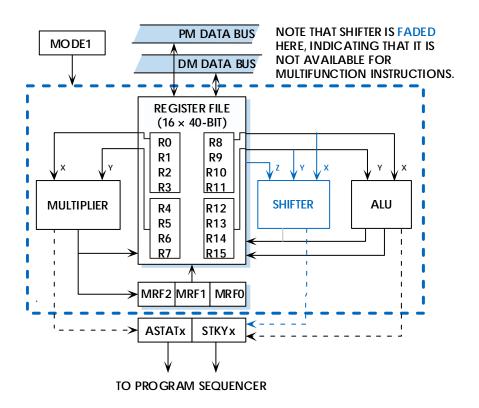

The processor core contains two processing elements (PEx and PEy). Each element contains a data register file and three independent computation units: an ALU, a multiplier with a fixed-point accumulator, and a shifter. For meeting a wide variety of processing needs, the computation units process data in three formats: 32-bit fixed-point, 32-bit floating-point and 40-bit floating-point.

The floating-point operations are single-precision IEEE-compatible. The 32-bit floating-point format is the standard IEEE format, whereas the 40-bit extended-precision format has eight additional Least Significant Bits (LSBs) of mantissa for greater accuracy.

The ALU performs a set of arithmetic and logic operations on both fixed-point and floating-point formats. The multiplier performs floating-point or fixed-point multiplication and fixed-point multiply/add or multiply/subtract operations. The shifter performs logical and arithmetic shifts, bit manipulation, field deposit and extraction, and exponent derivation operations on 32-bit operands. These computation units perform single-cycle operations; there is no computation pipeline. All units are connected in parallel, rather than serially. The output of any unit may serve as the input of any unit on the next cycle. In a multifunction computation, the ALU and multiplier perform independent, simultaneous operations.

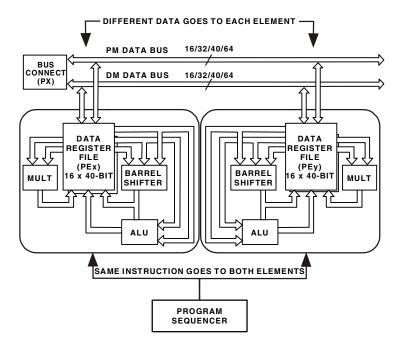

Each processing element has a general-purpose data register file that transfers data between the computation units and the data buses and stores intermediate results. A register file has two sets (primary and secondary) of sixteen registers each, for fast context switching. All of the registers are 40 bits wide. The register file, combined with the core processor's Super Harvard architecture, allows unconstrained data flow between computation units and internal memory. **Primary Processing Element (PEx).** PEx processes all computational instructions whether the processor is in Single-Instruction, Single-Data (SISD) or Single-Instruction, Multiple-Data (SIMD) mode. This element corresponds to the computational units and register file in previous ADSP-21000 family DSPs.

Secondary Processing Element (PEy). PEy processes each computational instruction in lock-step with PEx, but only processes these instructions when the processor is in SIMD mode. Because many operations are influenced by this mode, more information on SIMD is available in multiple locations:

- For information on PEy operations, see "Processing Elements" on page 2-1

- For information on data addressing in SIMD mode, see "Addressing in SISD and SIMD Modes" on page 4-18

- For information on data accesses in SIMD mode, see "SISD, SIMD, and Broadcast Load Modes" on page 5-51

- For information on multiprocessing in SIMD mode, see "Multiprocessor (MP) Interface" on page 7-87

- For information on SIMD programming, see the ADSP-21160 SHARC DSP Instruction Set Reference

#### Program Sequence Control

Internal controls for ADSP-21161 processor program execution come from four functional blocks: program sequencer, data address generators, timer, and instruction cache. Two dedicated address generators and a program sequencer supply addresses for memory accesses. Together the sequencer and data address generators allow computational operations to execute with maximum efficiency since the computation units can be devoted exclusively to processing data. With its instruction cache, the ADSP-21161 processor can simultaneously fetch an instruction from the cache and access two data operands from memory. The data address generators implement circular data buffers in hardware.

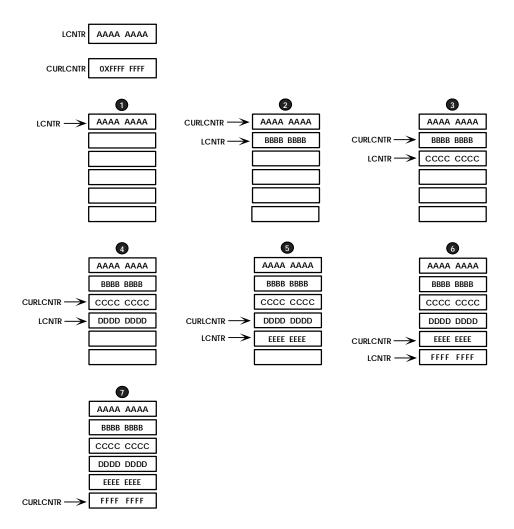

**Program Sequencer.** The program sequencer supplies instruction addresses to program memory. It controls loop iterations and evaluates conditional instructions. With an internal loop counter and loop stack, the ADSP-21161 processor executes looped code with zero overhead. No explicit jump instructions are required to loop or to decrement and test the counter.

The ADSP-21161 processor achieves its fast execution rate by means of pipelined fetch, decode, and execute cycles. If external memories are used, they are allowed more time to complete an access than if there were no decode cycle.

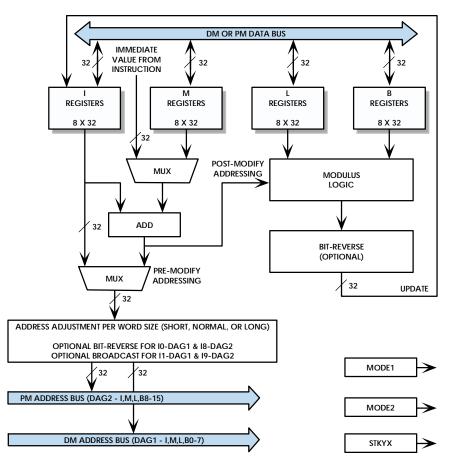

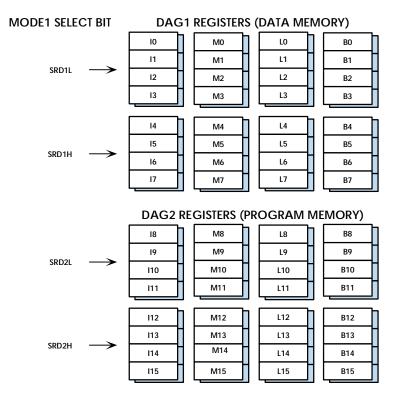

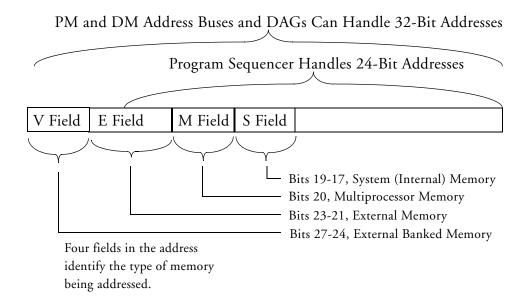

Data Address Generators. The Data Address Generators (DAGs) provide memory addresses when data is transferred between memory and registers. Dual data address generators enable the processor to output simultaneous addresses for two operand reads or writes. DAG1 supplies 32-bit addresses to data memory. DAG2 supplies 32-bit addresses to program memory for program memory data accesses.

Each DAG keeps track of up to eight address pointers, eight modifiers and eight length values. A pointer used for indirect addressing can be modified by a value in a specified register, either before (pre-modify) or after (post-modify) the access. A length value may be associated with each pointer to perform automatic modulo addressing for circular data buffers; the circular buffers can be located at arbitrary boundaries in memory. Each DAG register has a secondary register that can be activated for fast context switching. Circular buffers allow efficient implementation of delay lines and other data structures required in digital signal processing, and are commonly used in digital filters and Fourier transforms. The DAGs automatically handle address pointer wraparound, reducing overhead, increasing performance, and simplifying implementation.

Interrupts. The ADSP-21161 processor has four external hardware interrupts: three general-purpose interrupts, TRQ2-0, and a special interrupt for reset. The processor also has internally generated interrupts for the timer, DMA controller operations, circular buffer overflow, stack overflows, arithmetic exceptions, multiprocessor vector interrupts, and user-defined software interrupts.

For the general-purpose external interrupts and the internal timer interrupt, the ADSP-21161 processor automatically stacks the arithmetic status and mode (MODE1) registers in parallel with the interrupt servicing, allowing fifteen nesting levels of very fast service for these interrupts.

**Context Switch.** Many of the processor's registers have secondary registers that can be activated during interrupt servicing for a fast context switch. The data registers in the register file, the DAG registers, and the multiplier result register all have secondary registers. The primary registers are active at reset, while the secondary registers are activated by control bits in a mode control register.

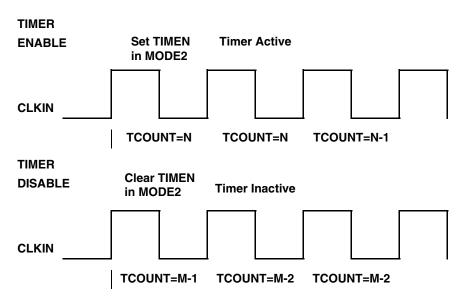

**Timer.** The programmable interval timer provides periodic interrupt generation. When enabled, the timer decrements a 32-bit count register every cycle. When this count register reaches zero, the ADSP-21161 processor generates an interrupt and asserts its timer expired output. The count register is automatically reloaded from a 32-bit period register and the count resumes immediately.

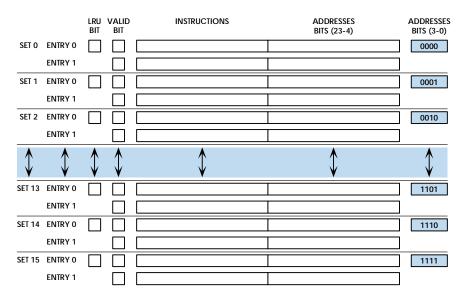

**Instruction Cache.** The program sequencer includes a 32-word instruction cache that enables three-bus operation for fetching an instruction and two data values. The cache is selective; only instructions whose fetches

conflict with program memory data accesses are cached. This caching allows full-speed execution of core, looped operations such as digital filter multiply-accumulates and FFT butterfly processing.

#### **Processor Internal Buses**

The processor core has six buses: PM address, PM data, DM address, DM data, IO address, and IO data. Due to processor's Super Harvard Architecture, data memory stores data operands, while program memory can store both instructions and data. This architecture allows dual data fetches, when the instruction is supplied by the cache.

**Bus Capacities.** The PM address bus and DM address bus transfer the addresses for instructions and data. The PM data bus and DM data bus transfer the data or instructions from each type of memory. the PM address bus is 32 bits wide, allowing access of up to 62 Mwords for non-SDRAM and 254 Mwords for SDRAM banks of mixed instructions and data. The PM data bus is 64 bits wide from (8-, 16-, and 32-bits) to accommodate the 48-bit instructions and 32-bit data.

The DM address bus is 32 bits wide allowing direct access of up to 4G words of data. The DM data bus is 64 bits wide. The DM data bus provides a path for the contents of any register in the processor to be transferred to any other register or to any data memory location in a single cycle. The data memory address comes from one of two sources: an absolute value specified in the instruction code (direct addressing) or the output of a data address generator (indirect addressing).

The IO address and IO data buses let the IO processor access internal memory for DMA without delaying the processor core. The IO address bus is 18 bits wide, and the IO data bus is 64 bits wide.

**Data Transfers.** Nearly every register in the processor core is classified as a Universal Register (UREG). Instructions allow transferring data between any two universal registers or between a universal register and memory. This support includes transfers between control registers, status registers,

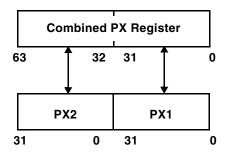

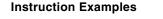

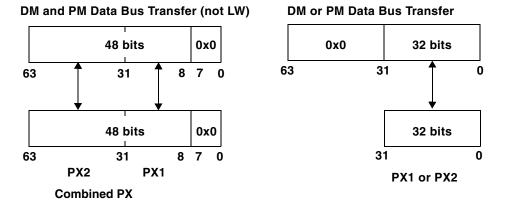

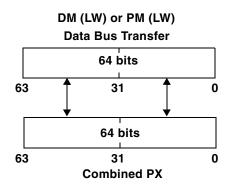

and data registers in the register file. The PM bus connect (PX) registers permit data to be passed between the 64-bit PM data bus and the 64-bit DM data bus, or between the 40-bit register file and the PM data bus. These registers contain hardware to handle the data width difference. For more information, see For more information, see "Processing Element Registers" on page A-23.

### **Processor Peripherals**

The term *processor peripherals* refers to everything outside the processor core. The ADSP-21161 processor peripherals include internal memory, external port, I/O processor, JTAG port, and any external devices that connect to the processor.

#### Dual-Ported Internal Memory (SRAM)

The ADSP-21161 processor contains 1 megabit of on-chip SRAM, organized as two blocks of 0.5 Mbits. Each block can be configured for different combinations of code and data storage. Each memory block is dual-ported for single-cycle, independent accesses by the core processor and I/O processor or DMA controller. The dual-ported memory and separate on-chip buses allow two data transfers from the core and one from I/O, all in a single cycle.

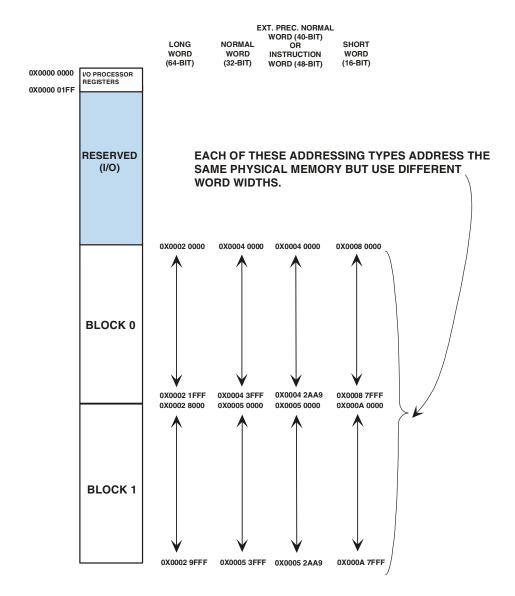

All of the memory can be accessed as 16-, 32-, 48-, or 64-bit words. On the ADSP-21161 processor, the memory can be configured as a maximum of 32K words of 32-bit data, 64K words of 16-bit data, 21.25K words of 48-bit instructions (and 40-bit data), or combinations of different word sizes up to 1.0 Mbit.

The processor supports a 16-bit floating-point storage format, which effectively doubles the amount of data that may be stored on chip. Conversion between the 32-bit floating-point and 16-bit floating-point formats completes in a single instruction.

While each memory block can store combinations of code and data, accesses are most efficient when one block stores data, using the DM bus for transfers, and the other block stores instructions and data, using the PM bus for transfers. Using the DM bus and PM bus in this way, with one dedicated to each memory block, assures single-cycle execution with two data transfers. In this case, the instruction must be available in the cache. The processor uses its external port to maintain single-cycle execution when one of the data operands is transferred to or from off-chip.

#### **External Port**

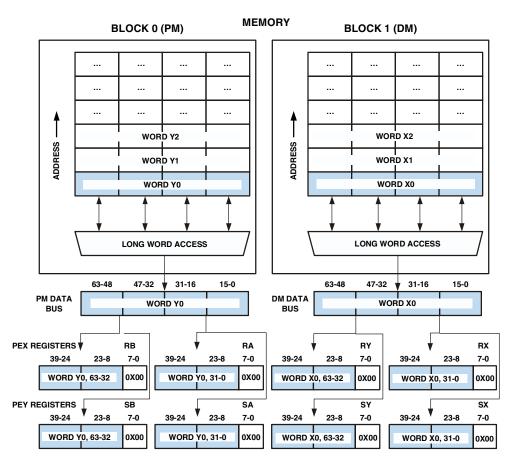

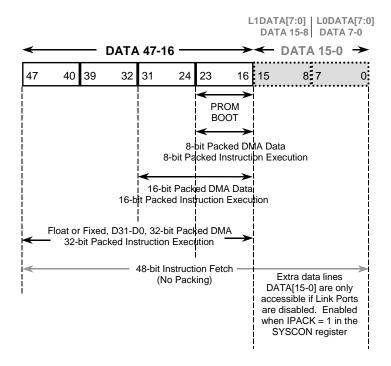

The ADSP-21161 processor external port provides the processor interface to off-chip memory and peripherals. The 254 Mword off-chip address space is included in the unified address space of the ADSP-21161 processor. The separate on-chip buses—for PM address, PM data, DM address, DM data, IO address, and IO data—multiplex at the external port to create an external system bus with a single 24-bit address bus and a single 32-bit data bus. The ADSP-21161 processor on-chip DMA controller automatically packs external data into the appropriate word width during transfers.

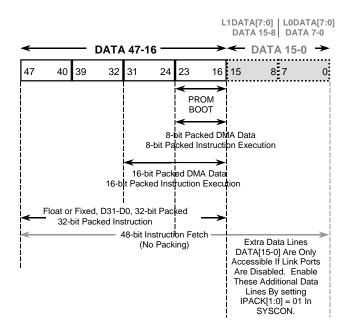

The ADSP-21161 processor supports instruction packing modes to execute from 48-, 32-, 16-, and 8-bit wide memories. With the link ports disabled, the additional link port pins can be used to execute 48-bit wide instructions. The ADSP-21161 processor also includes 32- to 48-bit, 16to 48-bit, 8- to 48-bit execution packing for executing instruction directly from 32-bit, 16-bit, or 8-bit wide external memories. External SDRAM, SRAM, or SBSRAM can be 8-, 16-, or 32-bits wide for DMA transfers to or from external memory.

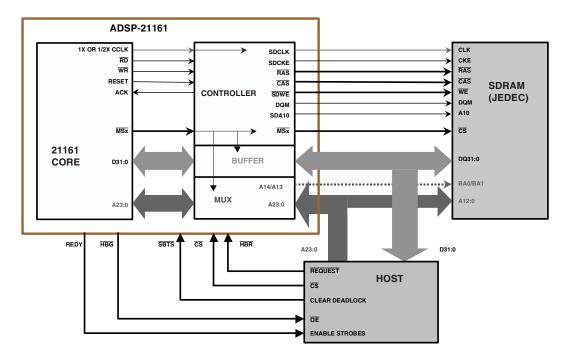

On-chip decoding of high-order address lines generates memory bank select signals for addressing external memory devices. The ADSP-21161 processor provides programmable memory waitstates and external memory acknowledge controls for interfacing to peripherals with variable access, hold, and disable time requirements. **SDRAM Interface.** The ADSP-21161 processor integrated on-chip SDRAM controller transfers data to and from synchronous DRAM (SDRAM) at the core clock frequency or one-half the core clock frequency. The synchronous approach, coupled with the core clock frequency, supports data transfer at a high throughput—up to 400 Mbytes/second for 32-bit transfers and 600 Mbytes/second for 48-bit transfers.

The SDRAM interface provides a glueless interface with standard SDRAMs—16 Mbits, 64 Mbits, 128 Mbits, and 256 Mbits—and includes options to support additional buffers between the ADSP-21161 processor and SDRAM. The SDRAM interface is extremely flexible and provides capability for connecting SDRAMs to any one of the ADSP-21161 processor four external memory banks, with up to all four banks mapped to SDRAM.

Systems with several SDRAM devices connected in parallel may require buffering to meet overall system timing requirements. The ADSP-21161 processor supports pipelining of the address and control signals to enable such buffering between itself and multiple SDRAM devices.

Host Processor Interface. The ADSP-21161 processor host interface allows easy connection to standard microprocessor buses, 8-bit, 16-bit and 32-bit, with little additional hardware required. The interface supports asynchronous and synchronous transfers at speeds up to the half the internal core clock rate of the ADSP-21161 processor. The host interface operates through the ADSP-21161 processor external port and maps into the unified address space. Four channels of DMA are available for the host interface; code and data transfers occur with low software overhead. The host can directly read and write the IOP register space of the ADSP-21161 processor and can access the DMA channel setup and mailbox registers. The host can also perform DMA transfers to and from the internal memory of the processor. Vector interrupt support provides for efficient execution of host commands. Multiprocessor System Interface. The ADSP-21161 processor offers powerful features tailored to multiprocessing systems. The unified address space allows direct interprocessor accesses of each ADSP-21161 processor internal IOP registers. Distributed bus arbitration logic on the processor allows simple, glueless connection of systems containing up to six ADSP-21161 processor and a host processor. Master processor changeover incurs only one cycle of overhead. Bus arbitration handles either fixed or rotating priority. Processor bus lock allows indivisible read-modify-write sequences for semaphores. A vector interrupt capability is provided for interprocessor commands.

#### I/O Processor

The ADSP-21161 processor Input/Output Processor (IOP) includes four serial ports, two link ports, a SPI-compatible port, and a DMA controller. One of the processes that the IO processor automates is booting. The processor can boot from the external port (with data from an 8-bit EPROM or a host processor) or a link port. Alternatively, a no-boot mode lets the processor start by executing instructions from external memory without booting.

**Serial Ports.** The ADSP-21161 processor features four synchronous serial ports that provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices. The serial ports can operate at up to half the processor core clock rate. Programmable data direction provides greater flexibility for serial communications. Serial port data can automatically transfer to and from on-chip memory using DMA. Each of the serial ports offers a TDM multichannel mode (up to 128 channels) and supports m-law or A-law companding. I<sup>2</sup>S support is also provided with the ADSP-21161 processor.

The serial ports can operate with little-endian or big-endian transmission formats, with word lengths from 3 to 32 bits. The serial ports offer select-able synchronization and transmit modes. Serial port clocks and frame syncs can be internally or externally generated.

#### INTRODUCTION

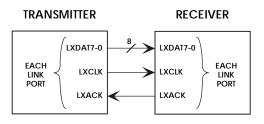

Link Ports. The ADSP-21161 processor features two 8-bit link ports that provide additional I/O capabilities. Link port I/O is especially useful for point-to-point interprocessor communication in multiprocessing systems. The link ports can operate independently and simultaneously. The data packs into 32-bit or 48-bit words, which the processor core can directly read or the IO processor can DMA-transfer to on-chip memory. Clock and acknowledge handshaking signals control link port transfers. Transfers are programmable as either transmit or receive.

Serial Peripheral (Compatible) Interface. The ADSP-21161 processor Serial Peripheral Interface (SPI) is an industry standard synchronous serial link that enables the ADSP-21161 processor SPI-compatible port to communicate with other SPI-compatible devices. SPI is a 4-wire interface consisting of two data pins, one device select pin, and one clock pin. It is a full-duplex synchronous serial interface, supporting both master and slave modes. It can operate in a multi-master environment by interfacing with up to four other SPI-compatible devices, either acting as a master or slave device. The ADSP-21161 processor SPI-compatible peripheral implementation also supports programmable baud rate and clock phase/polarities, and the use of open drain drivers to support the multi-master scenario to avoid data contention.

**DMA Controller.** The ADSP-21161 processor on-chip DMA controller allows zero-overhead data transfers without processor intervention. The DMA controller operates independently and invisibly to the processor core, allowing DMA operations to occur while the core is simultaneously executing its program. Both code and data can be downloaded to the ADSP-21161 processor using DMA transfers.

DMA transfers can occur between the ADSP-21161 processor internal memory and external memory, external peripherals, or a host processor. DMA transfers between external memory and external peripheral devices are another option. External bus packing to 8-, 16-, 32-, 48-, or 64-bit words is automatically performed during DMA transfers. Fourteen channels of DMA are available on the ADSP-21161 processor two over the link ports (shared with SPI), eight over the serial ports, and four over the processor's external port. The external port DMA channels serve for host processor, other ADSP-21161 processor DSPs, memory, or I/O transfers.

# JTAG Port

The JTAG port on the ADSP-21161 processor supports the IEEE standard 1149.1 Joint Test Action Group (JTAG) standard for system test. This standard defines a method for serially scanning the I/O status of each component in a system. Emulators use the JTAG port to monitor and control the processor during emulation. Emulators using this port provide full-speed emulation with access to inspect and modify memory, registers, and processor stacks. JTAG-based emulation is non-intrusive and does not effect target system loading or timing.

# Differences From Previous SHARC Processors

This section identifies differences between the ADSP-21161 processor and previous SHARC processors: ADSP-21160, ADSP-21060, ADSP-21061, ADSP-21062, and ADSP-21065. The ADSP-21161 processor preserves much of the ADSP-2106x architecture and is comparable to the ADSP-21160 with extended performance and functionality. For back-ground information on SHARC and the ADSP-2106x Family processors, see the ADSP-2106x SHARC User's Manual or the ADSP-21065L SHARC Technical Reference.

### **Processor Core Enhancements**

Computational bandwidth on the ADSP-21161 processor is significantly greater than that on the ADSP-2106x DSPs. The increase comes from raising the operational frequency and adding another processing element: ALU, shifter, multiplier, and register file. The new processing element lets the processor to process multiple data streams in parallel (SIMD mode).

Like the ADSP-21160, the program sequencer on the ADSP-21161 processor differs from the ADSP-2106x family, having several enhancements: new interrupt vector table definitions, SIMD mode stack and conditional execution model, and instruction decodes associated with new instructions. Interrupt vectors have been added that detect illegal memory accesses. Link port interrupt control has moved to a new register to support the additional DMA channels. Also, mode stack and mode mask support has been added to improve context switch time.

As with the ADSP-21160, the data address generators on the ADSP-21161 processor differ from the ADSP-2106x in that DAG2 (for the PM bus) has the same addressing capability as DAG1 (for the DM bus). The DAG registers move 64-bits per cycle. Additionally, the DAGs support the new memory map and Long Word transfer capability. Circular buffering on the ADSP-21161 processor can be quickly disabled on interrupts and restored on the return. Data "broadcast", from one memory location to both data register files, is determined by appropriate index register usage.

### **Processor Internal Bus Enhancements**

The PM, DM, and IO data buses on the ADSP-21161 processor have increased on the ADSP-2106x processors to 64 bits. Additional multiplexing and control logic on the ADSP-21161 processor enable 16-, 32-, or 64-bit wide moves between both register files and memory. The ADSP-21161 processor is capable of broadcasting a single memory location to each of the register files in parallel. Also, the ADSP-21161 processor permits register contents to be exchanged between the two processing elements' register files in a single cycle.

### **Memory Organization Enhancements**

The ADSP-21161 processor memory map differs from the ADSP-2106x's and is similar in organization to the ADSP-21160. The system memory map on the ADSP-21161 processor supports double-word transfers each cycle, reflects extended internal memory capacity for derivative designs, and works with updated control register for SIMD support.

### **External Port Enhancements**

The ADSP-21161 processor external port differs from the ADSP-2106x DSPs. The data bus on the ADSP-21160 is 32-bits wide. A new packing mode permits DMA for instructions and data to and from 8-bit external memory. The ADSP-21161 processor has a new synchronous interface that improves local bus switching frequency. Also, burst support on the ADSP-21161 processor improves bus usage.

#### Host Interface Enhancements

The ADSP-21161 processor host interface differs from the ADSP-2106x DSPs. It is 32-bit wide and supports 8-bit, 16- and 32-bit hosts. Although the ADSP-21161 processor supports the ADSP-2106x asynchronous host interface protocols, the ADSP-21161 processor also provides new synchronous interface protocols for maximum throughput.

The host/local bus deadlock resolution function on the ADSP-21161 processor is extended to the DMA controller. With this function the host (or bridge) logic forces the local bus to wait until the host completes it's operation.

#### **Multiprocessor Interface Enhancements**

The ADSP-21161 processor multiprocessor system interface supports greater throughput than the ADSP-2106x DSPs. The throughput between ADSP-21161 processors in a multiprocessing application increases due to new shared bus transfer protocols, shared bus cycle time improvements due to synchronous interface, and improvements in link port throughput. The external port supports glueless multiprocessing, with distributed arbitration for up to six ADSP-21161 processors.

# **IO Architecture Enhancements**

The IO processor on the ADSP-21161 processor provides much greater throughput than the ADSP-2106x DSPs. This section describes how the link ports and DMA controller differ on the ADSP-21161 processor.

#### **DMA Controller Enhancements**

The ADSP-21161 processor DMA controller supports 14 channels compared to 10 on the ADSP-2106x DSPs. New packing modes support the 64-bit internal busing. To resolve potential deadlock scenarios, the ADSP-21161 processor DMA controller relinquishes the local bus in a similar fashion to the processor core when host logic asserts both  $\overline{\text{HBR}}$  and  $\overline{\text{SBTS}}$ .

#### Link Port Enhancements

The ADSP-21161 processor two link ports provide greater throughput than the ADSP-2106x DSPs. The link port data bus width on the ADSP-21161 processor is 8 bits wide (versus 4 bits on the ADSP-2106x DSPs). Link port clock control on the ADSP-21161 processor supports a wider frequency range.

# **Instruction Set Enhancements**

ADSP-21161 processor provides source code compatibility with the previous SHARC family members, to the application assembly source code level. All instructions, control registers, and system resources available in the ADSP-2106x core programming model are available in ADSP-21161 processor. Instructions, control registers, or other facilities, required to support the new feature set of ADSP-2116x core include the following.

- Code compatible to the ADSP-21160 SIMD core

- Supersets of the ADSP-2106x programming model

- Reserved facilities in the ADSP-2106x programming model

- Symbol name changes from the ADSP-2106x and ADSP-21161 processor programming models

These name changes can be managed through re-assembly using the ADSP-21161 processor development tools to apply the ADSP-21161 processor symbol definitions header file and linker description file. While these changes have no direct impact on existing core applications, system and I/O processor initialization code and control code do require modifications.

Although the porting of source code written for the ADSP-2106x family to ADSP-21161 processor has been simplified, code changes are required to take full advantage of the new ADSP-21161 processor features. For more information, see the *ADSP-21160 SHARC DSP Instruction Set Reference*.

# For More Information About Analog Products

Analog Devices is online on the internet at http://www.analog.com. Our web pages provide information on the company and products, including access to technical information and documentation, product overviews, and product announcements.

Additional information may be obtained about Analog Devices and its products in any of the following ways:

- Visit our World Wide Web site at www.analog.com

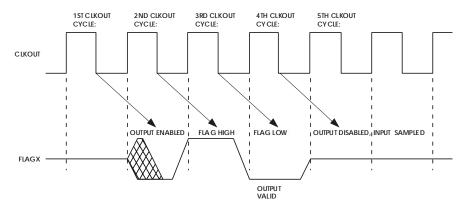

- FAX questions or requests for information to 1(781)461-3010.